|

PandA-2024.02

|

|

PandA-2024.02

|

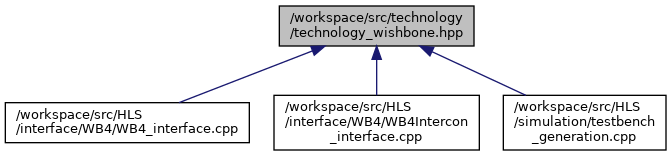

Utility header to access wishbone technology library. More...

Go to the source code of this file.

Macros | |

| #define | WBLIBRARY "WBWrapper" |

| #define | ADDRESS_RANGE_CHECKER_WB "address_range_checker_FU" |

| #define | ADDRESS_FILTER_WB "address_filter_FU" |

| #define | SEL_CONVERTER_WB "sel_converter_FU" |

| #define | DATARAMSIZE_CONVERTER_WB "dataramsize_converter_FU" |

| #define | REGISTER_WADDRESS_WB "register_waddress_FU" |

| #define | WISHBONE_START_CONTROLLER_WB "wishbone_start_controller_FU" |

| #define | NOT_INTERNAL_COMPONENT "not_internal_component" |

| #define | NOTIFY_CALLER "notify_caller_FU" |

| #define | WB4_INTERCON "wb4Intercon" |

| #define | WB_DATIM_PORT_NAME "dat_im" |

| #define | WB_ACKIM_PORT_NAME "ack_im" |

| #define | WB_CYCOM_PORT_NAME "cyc_om" |

| #define | WB_STBOM_PORT_NAME "stb_om" |

| #define | WB_WEOM_PORT_NAME "we_om" |

| #define | WB_ADDROM_PORT_NAME "addr_om" |

| #define | WB_DATOM_PORT_NAME "dat_om" |

| #define | WB_SELOM_PORT_NAME "sel_om" |

| #define | WB_CYCIS_PORT_NAME "cyc_is" |

| #define | WB_STBIS_PORT_NAME "stb_is" |

| #define | WB_WEIS_PORT_NAME "we_is" |

| #define | WB_ADDRIS_PORT_NAME "addr_is" |

| #define | WB_DATIS_PORT_NAME "dat_is" |

| #define | WB_SELIS_PORT_NAME "sel_is" |

| #define | WB_DATOS_PORT_NAME "dat_os" |

| #define | WB_ACKOS_PORT_NAME "ack_os" |

| #define | WB_IRQ_PORT_NAME "irq" |

| #define | WB_BASE_ADDRESS "BASE_ADDRESS" |

Utility header to access wishbone technology library.

Definition in file technology_wishbone.hpp.

| #define ADDRESS_FILTER_WB "address_filter_FU" |

Definition at line 50 of file technology_wishbone.hpp.

Referenced by WB4_interface::build_WB4_complete_logic().

| #define ADDRESS_RANGE_CHECKER_WB "address_range_checker_FU" |

Definition at line 49 of file technology_wishbone.hpp.

Referenced by WB4_interface::build_WB4_complete_logic().

| #define DATARAMSIZE_CONVERTER_WB "dataramsize_converter_FU" |

Definition at line 52 of file technology_wishbone.hpp.

Referenced by WB4_interface::build_WB4_complete_logic().

| #define NOT_INTERNAL_COMPONENT "not_internal_component" |

Definition at line 55 of file technology_wishbone.hpp.

Referenced by WB4_interface::build_WB4_complete_logic().

| #define NOTIFY_CALLER "notify_caller_FU" |

Definition at line 56 of file technology_wishbone.hpp.

| #define REGISTER_WADDRESS_WB "register_waddress_FU" |

Definition at line 53 of file technology_wishbone.hpp.

| #define SEL_CONVERTER_WB "sel_converter_FU" |

Definition at line 51 of file technology_wishbone.hpp.

Referenced by WB4_interface::build_WB4_complete_logic().

| #define WB4_INTERCON "wb4Intercon" |

Definition at line 57 of file technology_wishbone.hpp.

Referenced by buildCircuit().

| #define WB_ACKIM_PORT_NAME "ack_im" |

Definition at line 61 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_ACKOS_PORT_NAME "ack_os" |

Definition at line 78 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_ADDRIS_PORT_NAME "addr_is" |

Definition at line 73 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_ADDROM_PORT_NAME "addr_om" |

Definition at line 66 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_BASE_ADDRESS "BASE_ADDRESS" |

Definition at line 83 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), WB4_interface::build_WB4_complete_logic(), and buildCircuit().

| #define WB_CYCIS_PORT_NAME "cyc_is" |

Definition at line 70 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_CYCOM_PORT_NAME "cyc_om" |

Definition at line 63 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), WB4_interface::build_WB4_complete_logic(), and buildCircuit().

| #define WB_DATIM_PORT_NAME "dat_im" |

Definition at line 60 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_DATIS_PORT_NAME "dat_is" |

Definition at line 74 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_DATOM_PORT_NAME "dat_om" |

Definition at line 67 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_DATOS_PORT_NAME "dat_os" |

Definition at line 77 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_IRQ_PORT_NAME "irq" |

Definition at line 80 of file technology_wishbone.hpp.

Referenced by WB4_interface::build_WB4_bus_interface(), WB4_interface::build_WB4_complete_logic(), and buildCircuit().

| #define WB_SELIS_PORT_NAME "sel_is" |

Definition at line 75 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_SELOM_PORT_NAME "sel_om" |

Definition at line 68 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_STBIS_PORT_NAME "stb_is" |

Definition at line 71 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_STBOM_PORT_NAME "stb_om" |

Definition at line 64 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_WEIS_PORT_NAME "we_is" |

Definition at line 72 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WB_WEOM_PORT_NAME "we_om" |

Definition at line 65 of file technology_wishbone.hpp.

Referenced by build_bus_interface(), WB4_interface::build_WB4_bus_interface(), and WB4_interface::build_WB4_complete_logic().

| #define WBLIBRARY "WBWrapper" |

Definition at line 46 of file technology_wishbone.hpp.

Referenced by WB4_interface::build_WB4_complete_logic(), and buildCircuit().

| #define WISHBONE_START_CONTROLLER_WB "wishbone_start_controller_FU" |

Definition at line 54 of file technology_wishbone.hpp.

1.8.13

1.8.13