|

PandA-2024.02

|

|

PandA-2024.02

|

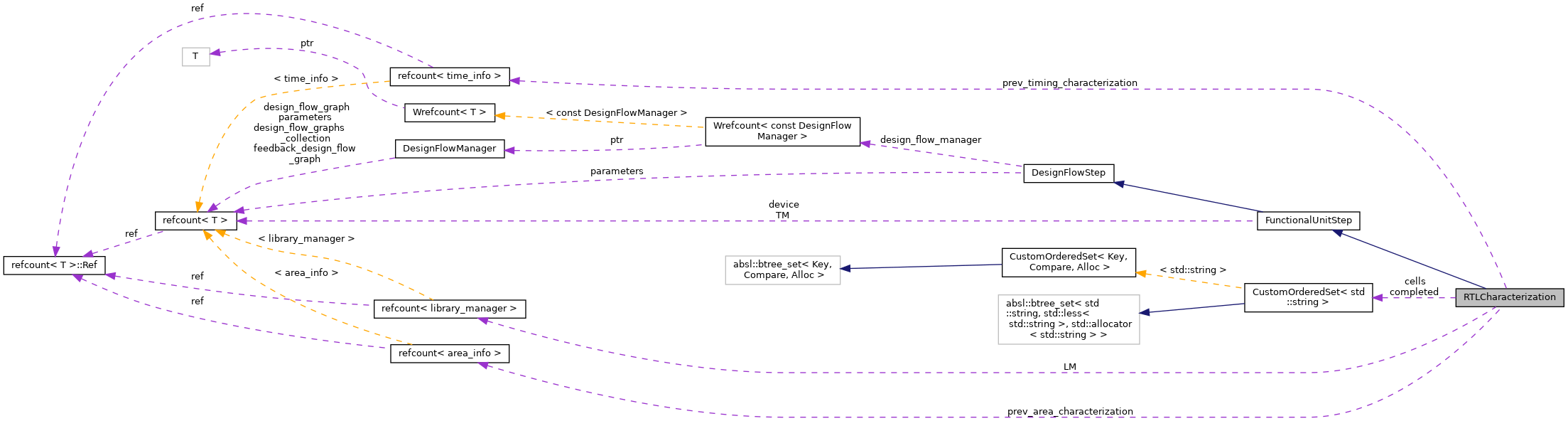

#include <RTL_characterization.hpp>

Public Member Functions | |

| RTLCharacterization (const generic_deviceRef _device, const std::string &_cells, const DesignFlowManagerConstRef design_flow_manager, const ParameterConstRef parameters) | |

| Constructor. More... | |

| ~RTLCharacterization () override | |

| Destructor. More... | |

| DesignFlowStep_Status | Exec () override |

| Perform RTL characterization of the modules with respect to the target device. More... | |

| bool | HasToBeExecuted () const override |

| Check if this step has actually to be executed. More... | |

| std::string | GetSignature () const override |

| Return a unified identifier of this design step. More... | |

| std::string | GetName () const override |

| Return the name of this design step. More... | |

| void | ComputeRelationships (DesignFlowStepSet &relationship, const DesignFlowStep::RelationshipType relationship_type) override |

| Compute the relationships of a step with other steps. More... | |

| DesignFlowStepFactoryConstRef | CGetDesignFlowStepFactory () const override |

| Return the factory to create this type of steps. More... | |

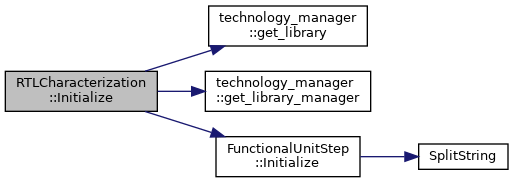

| void | Initialize () override |

| Initialize the step (i.e., like a constructor, but executed just before exec. More... | |

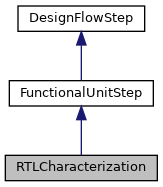

Public Member Functions inherited from FunctionalUnitStep Public Member Functions inherited from FunctionalUnitStep | |

| FunctionalUnitStep (const generic_deviceRef _device, const DesignFlowManagerConstRef design_flow_manager, const ParameterConstRef parameters) | |

| Constructor. More... | |

| ~FunctionalUnitStep () override | |

| Destructor. More... | |

Public Member Functions inherited from DesignFlowStep Public Member Functions inherited from DesignFlowStep | |

| DesignFlowStep (const DesignFlowManagerConstRef design_flow_manager, const ParameterConstRef parameters) | |

| Constructor. More... | |

| virtual | ~DesignFlowStep () |

| Destructor. More... | |

| DesignFlowStep_Status | GetStatus () const |

| Return the status of this design step. More... | |

| virtual void | WriteDot (std::ostream &out) const |

| Write the label for a dot graph. More... | |

| bool | IsComposed () const |

| Returns if this step is composed. More... | |

| int | CGetDebugLevel () const |

| Return the debug level of the step. More... | |

| virtual void | PrintInitialIR () const |

| Dump the initial intermediate representation. More... | |

| virtual void | PrintFinalIR () const |

| Dump the final intermediate representation. More... | |

Private Member Functions | |

| void | characterize_fu (const technology_nodeRef functional_unit) |

| Characterize the given functional unit with respect to the target device. More... | |

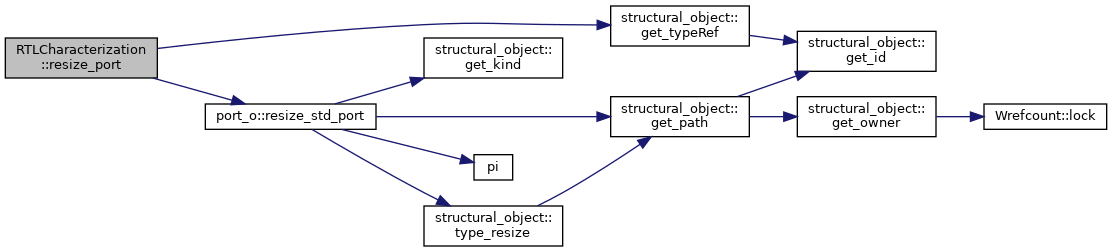

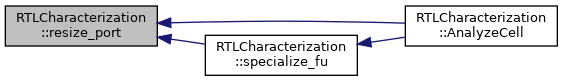

| void | resize_port (const structural_objectRef &port, unsigned int prec) |

| resize the port w.r.t a given precision More... | |

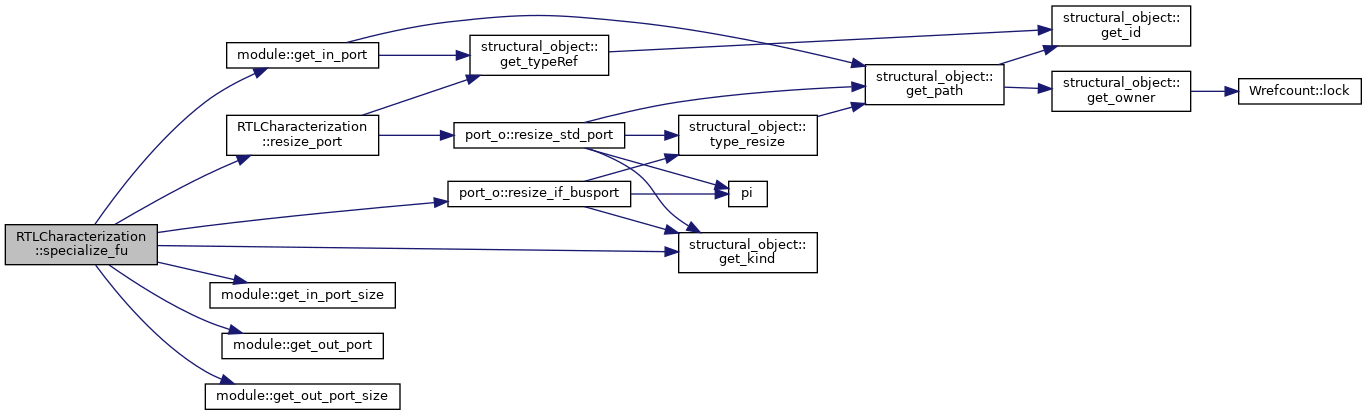

| void | specialize_fu (const module *mod, unsigned int prec, unsigned int bus_data_bitsize, unsigned int bus_addr_bitsize, unsigned int bus_size_bitsize, unsigned int bus_tag_bitsize, size_t portsize_value) |

| Performing the specialization of the given object. More... | |

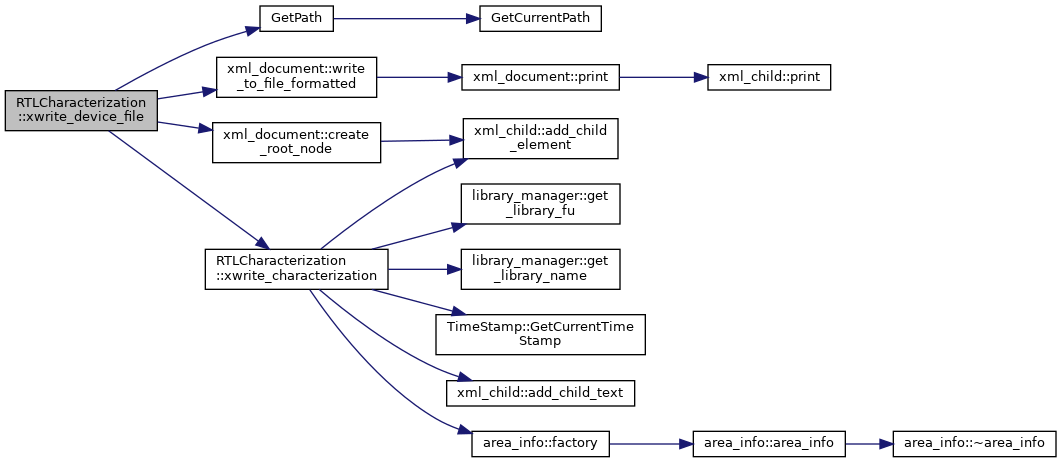

| void | xwrite_device_file () |

| Generate the output file. More... | |

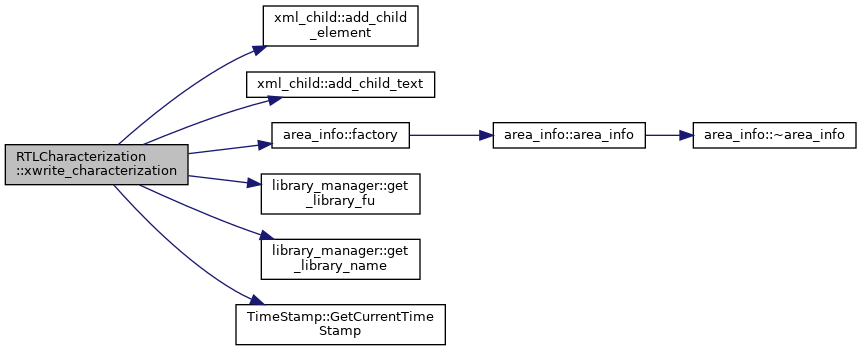

| void | xwrite_characterization (xml_element *nodeRoot) |

| Add the characterization to the output file. More... | |

| void | fix_execution_time_std () |

| Fix the execution time by removing set/hold/pad timings. More... | |

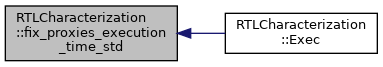

| void | fix_proxies_execution_time_std () |

| Fix execution/stage period value for proxies and bounded memory controllers. More... | |

| void | fix_muxes () |

| fix the estimation of mux timing More... | |

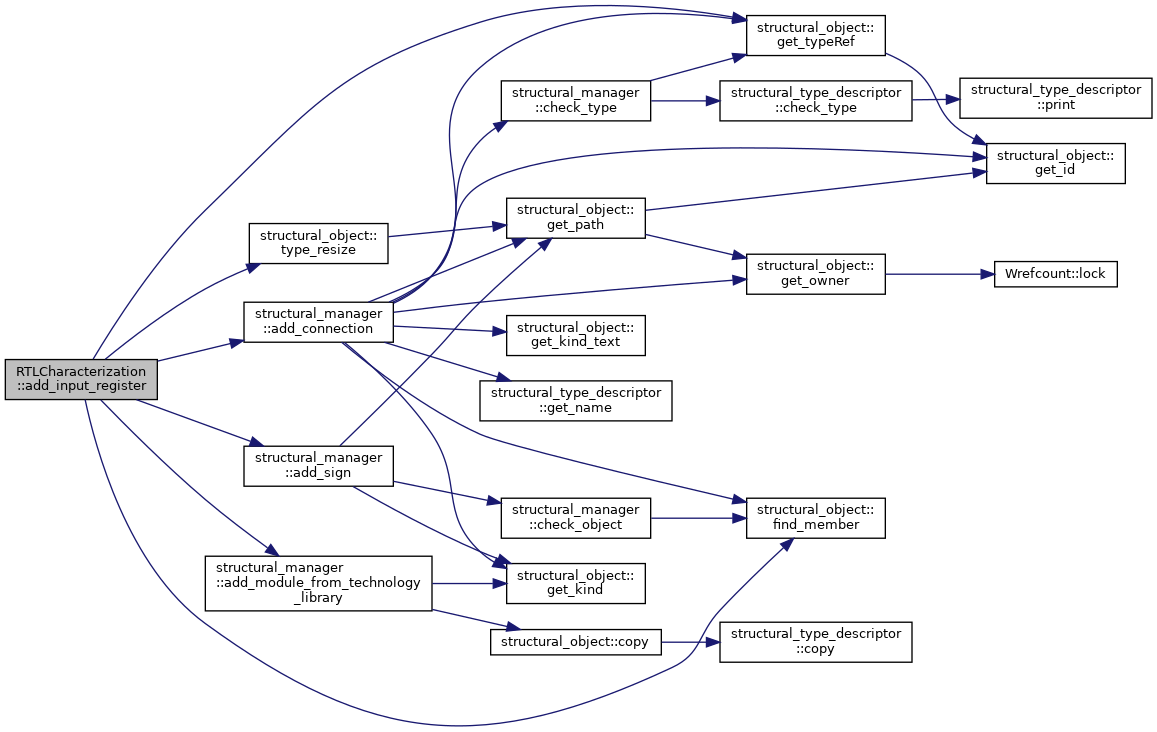

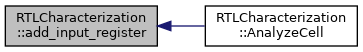

| void | add_input_register (structural_objectRef port_in, const std::string ®ister_library, const std::string &port_prefix, structural_objectRef reset_port, structural_objectRef circuit, structural_objectRef clock_port, structural_objectRef e_port, structural_managerRef SM) |

| void | add_output_register (structural_managerRef SM, structural_objectRef e_port, structural_objectRef circuit, structural_objectRef reset_port, structural_objectRef port_out, const std::string &port_prefix, structural_objectRef clock_port, const std::string ®ister_library) |

| const std::string | ComputeComponent (const std::string &input) const |

| Extract the component name from list of cells. More... | |

| const CustomSet< std::string > | ComputeCells (const std::string &input) const |

| Extract the cell lists. More... | |

| void | AnalyzeCell (functional_unit *fu, const unsigned int prec, const std::vector< std::string > &portsize_parameters, const size_t portsize_index, const std::vector< std::string > &pipe_parameters, const size_t stage_index, const unsigned int constPort, const bool is_commutative, size_t max_lut_size) override |

| Analyze the single cell. More... | |

Private Attributes | |

| library_managerRef | LM |

| Library manager. More... | |

| const std::string | component |

| The component to be characterized. More... | |

| const CustomSet< std::string > | cells |

| The cells to be characterized. More... | |

| area_infoRef | prev_area_characterization |

| The area model of the last characterization. More... | |

| time_infoRef | prev_timing_characterization |

| The time model of the last characterization. More... | |

| const bool | dummy_synthesis |

| True if we are performing dummy synthesis. More... | |

| CustomOrderedSet< std::string > | completed |

| set of units completed with success More... | |

Additional Inherited Members | |

Public Types inherited from DesignFlowStep Public Types inherited from DesignFlowStep | |

| enum | RelationshipType { DEPENDENCE_RELATIONSHIP, INVALIDATION_RELATIONSHIP, PRECEDENCE_RELATIONSHIP } |

| The relationship type. More... | |

Protected Member Functions inherited from FunctionalUnitStep Protected Member Functions inherited from FunctionalUnitStep | |

| virtual void | AnalyzeFu (const technology_nodeRef f_unit) |

| Analyze all the cells built starting from a template. More... | |

| technology_nodeRef | create_template_instance (const technology_nodeRef &fu_template, const std::string &name, unsigned int prec) |

| Create a template instance to be specialized. More... | |

Protected Attributes inherited from FunctionalUnitStep Protected Attributes inherited from FunctionalUnitStep | |

| const technology_managerRef | TM |

| Technology manager. More... | |

| const generic_deviceRef | device |

| device information More... | |

| unsigned int | has_first_synthesis_id |

| The id of the first analyzed cell of a sequence of cells which differ for the position of the constant. More... | |

| CustomMap< unsigned int, unsigned int > | DSP_y_to_DSP_x |

| The sizes of available DSPs. More... | |

Protected Attributes inherited from DesignFlowStep Protected Attributes inherited from DesignFlowStep | |

| bool | composed |

| True if this step represents a composition of design flow steps (e.g., a flow); must be set by specialized constructors. More... | |

| const Wrefcount< const DesignFlowManager > | design_flow_manager |

| The design flow manager. More... | |

| const ParameterConstRef | parameters |

| Set of input parameters. More... | |

| int | debug_level |

| The debug level. More... | |

| const int | output_level |

| The output level. More... | |

Definition at line 71 of file RTL_characterization.hpp.

| RTLCharacterization::RTLCharacterization | ( | const generic_deviceRef | _device, |

| const std::string & | _cells, | ||

| const DesignFlowManagerConstRef | design_flow_manager, | ||

| const ParameterConstRef | parameters | ||

| ) |

Constructor.

| _device | is the device |

| _cells | is the component to be characterized |

| design_flow_manager | is the design flow manager |

| parameters | is the set of input parameters |

Definition at line 82 of file RTL_characterization.cpp.

References DesignFlowStep::debug_level, GET_CLASS, DesignFlowStep::parameters, and ~RTLCharacterization().

|

overridedefault |

|

private |

Definition at line 629 of file RTL_characterization.cpp.

References structural_manager::add_connection(), structural_manager::add_module_from_technology_library(), structural_manager::add_sign(), CLOCK_PORT_NAME, structural_object::find_member(), GET_TYPE_SIZE, structural_object::get_typeRef(), structural_type_descriptor::INT, port_o_K, structural_type_descriptor::REAL, register_AR_NORETIME, register_AR_NORETIME_INT, register_AR_NORETIME_REAL, register_AR_NORETIME_UINT, RESET_PORT_NAME, FunctionalUnitStep::TM, structural_type_descriptor::type, structural_object::type_resize(), and structural_type_descriptor::UINT.

Referenced by AnalyzeCell().

|

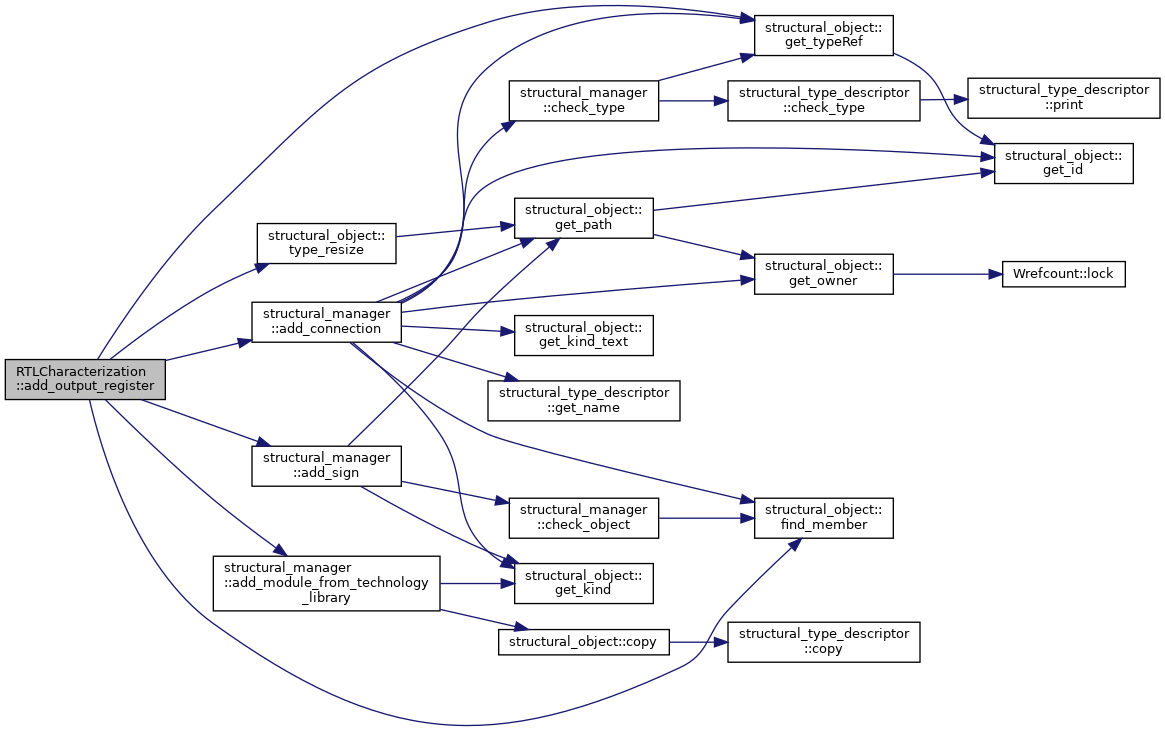

private |

Definition at line 677 of file RTL_characterization.cpp.

References structural_manager::add_connection(), structural_manager::add_module_from_technology_library(), structural_manager::add_sign(), CLOCK_PORT_NAME, structural_object::find_member(), GET_TYPE_SIZE, structural_object::get_typeRef(), structural_type_descriptor::INT, port_o_K, structural_type_descriptor::REAL, register_AR_NORETIME, register_AR_NORETIME_INT, register_AR_NORETIME_REAL, register_AR_NORETIME_UINT, RESET_PORT_NAME, FunctionalUnitStep::TM, structural_type_descriptor::type, structural_object::type_resize(), and structural_type_descriptor::UINT.

Referenced by AnalyzeCell().

|

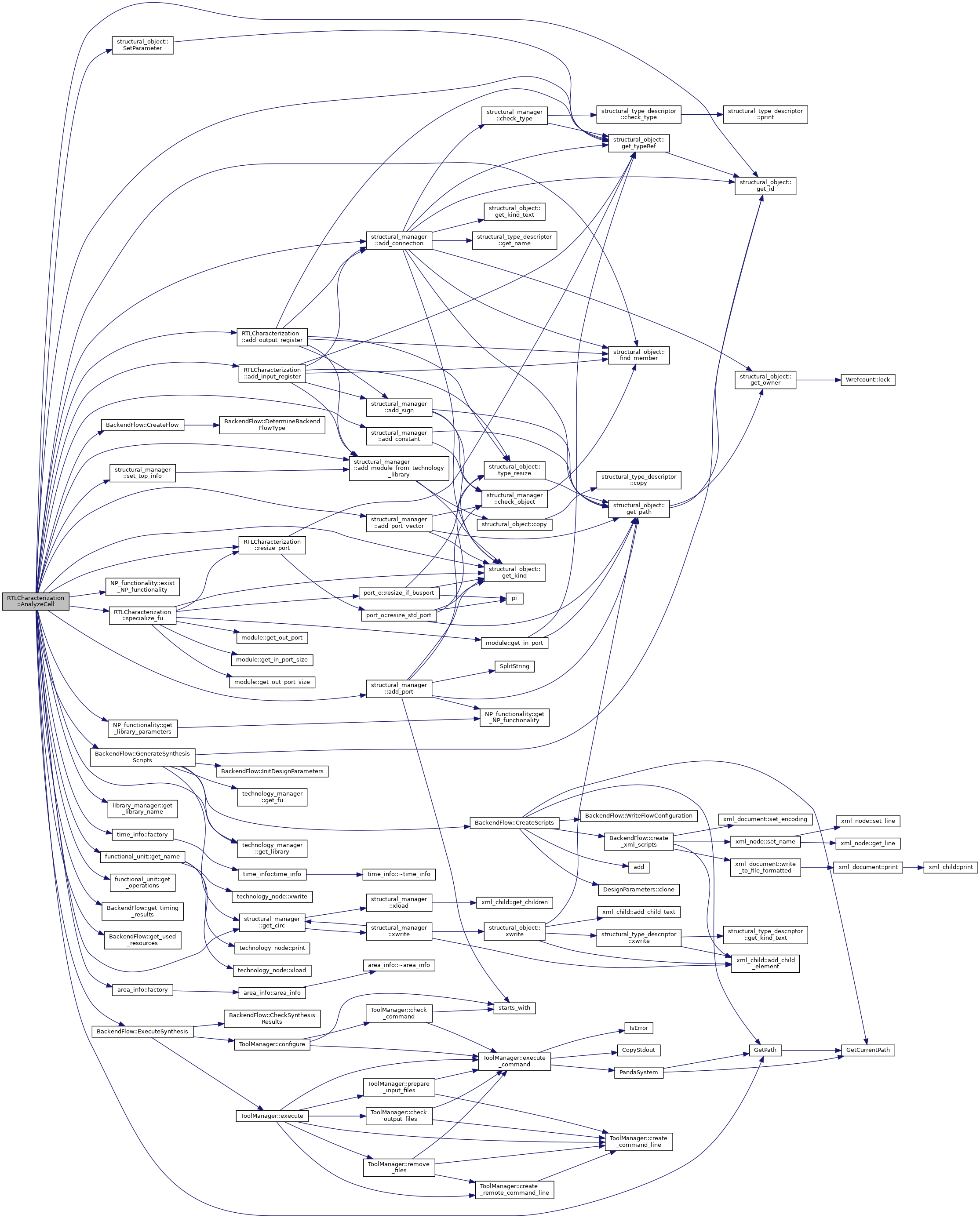

overrideprivatevirtual |

Analyze the single cell.

| fu | is the cell |

| prec | is the precision |

| portsize_parameters | is the size of parameters |

| portsize_index | |

| pipe_parameters | |

| constPort | is the index of the constant port |

| is_commutative | is true if all the operations are commutative |

some modules has to be characterized with respect to a different constant value

main circuit type

setting top circuit component

add further specializations for this module

add clock and reset

add register on inputs

add register on outputs

generate the synthesis scripts

the synthesis has been successfully completed setting the used resources

setting the timing values for each operation

Implements FunctionalUnitStep.

Definition at line 777 of file RTL_characterization.cpp.

References structural_manager::add_connection(), structural_manager::add_constant(), add_input_register(), structural_manager::add_module_from_technology_library(), add_output_register(), structural_manager::add_port(), structural_manager::add_port_vector(), functional_unit::area_m, cells, functional_unit::channels_type, CHANNELS_TYPE_MEM_ACC_11, CHANNELS_TYPE_MEM_ACC_N1, CHANNELS_TYPE_MEM_ACC_NN, functional_unit::characterizing_constant_value, CLOCK_PORT_NAME, completed, counter, BackendFlow::CreateFlow(), time_info::cycles_time_DEFAULT, FunctionalUnitStep::device, dummy_synthesis, BackendFlow::ExecuteSynthesis(), time_info::execution_time_DEFAULT, NP_functionality::exist_NP_functionality(), time_info::factory(), area_info::factory(), structural_object::find_member(), NP_functionality::FLOPOCO_PROVIDED, functional_unit::fu_template_name, functional_unit::fu_template_parameters, functional_unit::functional_unit_name, BackendFlow::GenerateSynthesisScripts(), structural_manager::get_circ(), structural_object::get_id(), structural_object::get_kind(), technology_manager::get_library(), library_manager::get_library_name(), NP_functionality::get_library_parameters(), functional_unit::get_name(), functional_unit::get_operations(), BackendFlow::get_timing_results(), structural_object::get_typeRef(), BackendFlow::get_used_resources(), GetPath(), FunctionalUnitStep::has_first_synthesis_id, time_info::initiation_time_DEFAULT, LM, LUT_EXPR_STD, max, MEMLOAD_STD, functional_unit::memory_type, MEMORY_TYPE_ASYNCHRONOUS, MEMORY_TYPE_SYNCHRONOUS_SDS, MEMORY_TYPE_SYNCHRONOUS_SDS_BUS, MEMORY_TYPE_SYNCHRONOUS_UNALIGNED, MEMSTORE_STD, DesignFlowStep::output_level, OUTPUT_LEVEL_VERBOSE, param, DesignFlowStep::parameters, lenet_tvm::params, PIPE_PARAMETER, port_o_K, PORT_VECTOR_N_PORTS, port_vector_o_K, prev_area_characterization, prev_timing_characterization, PRINT_OUT_MEX, register_AR_NORETIME, RESET_PORT_NAME, resize_port(), structural_manager::set_top_info(), structural_object::SetParameter(), specialize_fu(), time_info::stage_period_DEFAULT, START_PORT_NAME, STR, NP_functionality::SYSTEM_VERILOG_PROVIDED, THROW_ASSERT, FunctionalUnitStep::TM, NP_functionality::VERILOG_PROVIDED, and NP_functionality::VHDL_PROVIDED.

|

overridevirtual |

Return the factory to create this type of steps.

Implements DesignFlowStep.

Definition at line 771 of file RTL_characterization.cpp.

References THROW_UNREACHABLE.

|

private |

Characterize the given functional unit with respect to the target device.

|

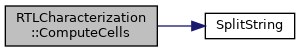

private |

Extract the cell lists.

| input | is the input string |

Definition at line 1332 of file RTL_characterization.cpp.

References component, SplitString(), and THROW_ASSERT.

|

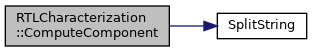

private |

Extract the component name from list of cells.

| input | is the input string |

Definition at line 1323 of file RTL_characterization.cpp.

References input, SplitString(), and THROW_ASSERT.

|

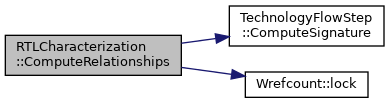

overridevirtual |

Compute the relationships of a step with other steps.

| dependencies | is where relationships will be stored |

| relationship_type | is the type of relationship to be computed |

Implements DesignFlowStep.

Definition at line 739 of file RTL_characterization.cpp.

References TechnologyFlowStep::ComputeSignature(), DesignFlowStep::DEPENDENCE_RELATIONSHIP, DesignFlowStep::design_flow_manager, DesignFlowStep::INVALIDATION_RELATIONSHIP, LOAD_TECHNOLOGY, Wrefcount< T >::lock(), DesignFlowStep::PRECEDENCE_RELATIONSHIP, and THROW_UNREACHABLE.

|

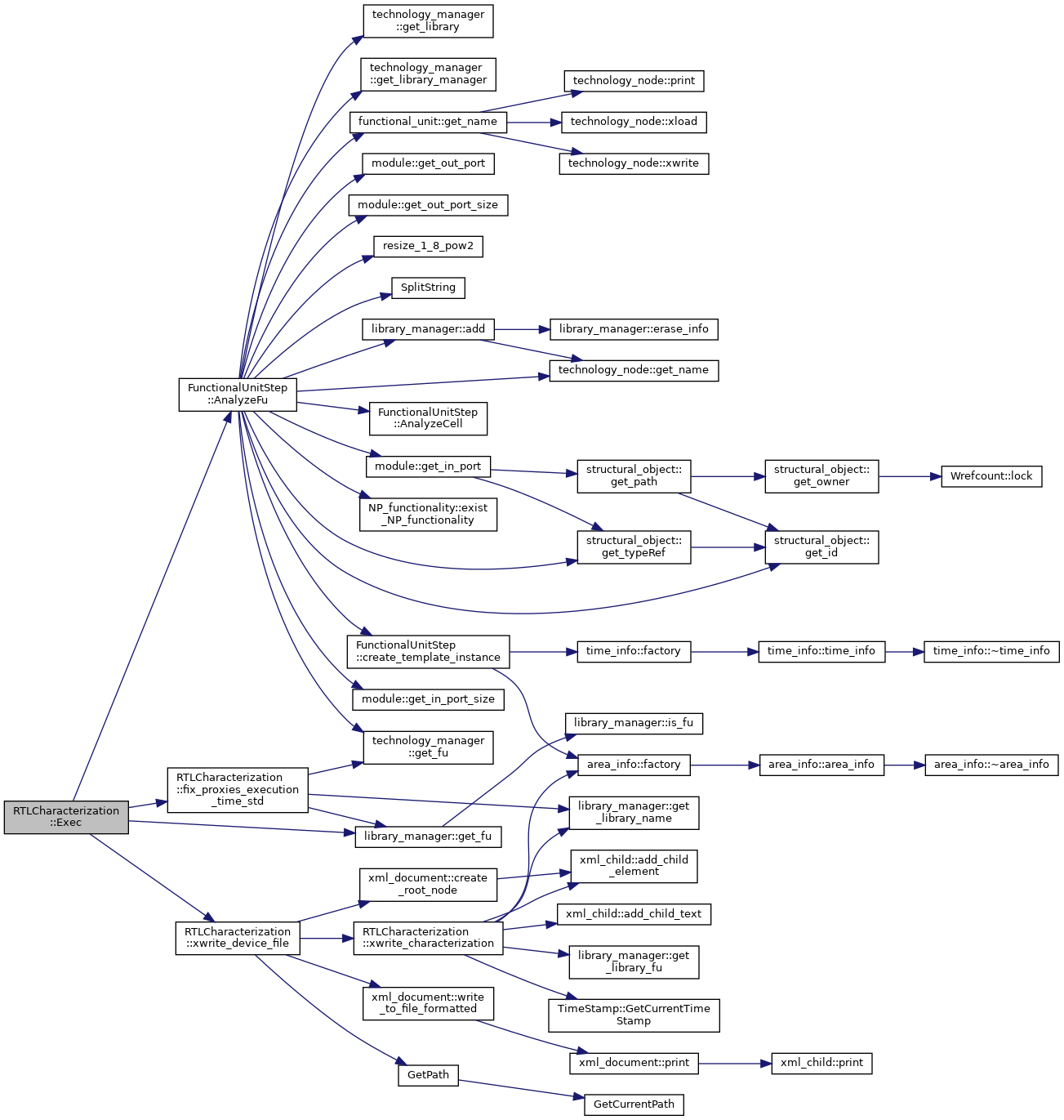

overridevirtual |

Perform RTL characterization of the modules with respect to the target device.

Implements DesignFlowStep.

Definition at line 108 of file RTL_characterization.cpp.

References FunctionalUnitStep::AnalyzeFu(), component, fix_proxies_execution_time_std(), library_manager::get_fu(), LM, SUCCESS, and xwrite_device_file().

|

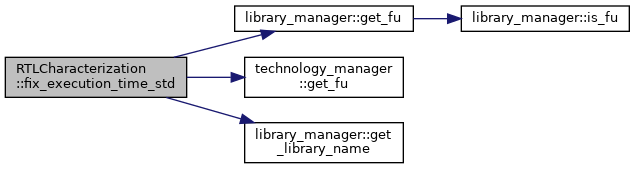

private |

Fix the execution time by removing set/hold/pad timings.

Definition at line 177 of file RTL_characterization.cpp.

References ASSIGN, ASSIGN_VECTOR_BOOL_STD, completed, component, library_manager::get_fu(), technology_manager::get_fu(), library_manager::get_library_name(), LIBRARY_PC, LIBRARY_STD, LIBRARY_STD_FU, LM, DesignFlowStep::parameters, and FunctionalUnitStep::TM.

|

private |

fix the estimation of mux timing

Definition at line 119 of file RTL_characterization.cpp.

References ASSIGN, ASSIGN_VECTOR_BOOL_STD, technology_manager::get_fu(), LIBRARY_STD_FU, MULTIPLIER_STD, MUX_GATE_STD, STR, TEST_MUL_MUX_8, and FunctionalUnitStep::TM.

|

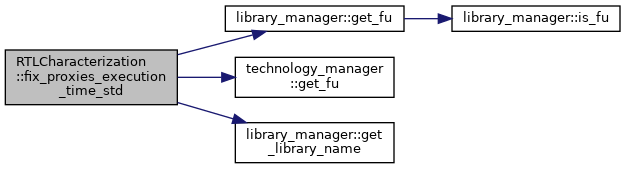

private |

Fix execution/stage period value for proxies and bounded memory controllers.

Definition at line 220 of file RTL_characterization.cpp.

References ARRAY_1D_STD_BRAM, ARRAY_1D_STD_BRAM_NN, BMEMORY_STD, BMEMORY_STDN, completed, component, library_manager::get_fu(), technology_manager::get_fu(), library_manager::get_library_name(), LIBRARY_PC, LIBRARY_STD, LIBRARY_STD_FU, LM, MEMORY_CTRL_TYPE_DPROXY, MEMORY_CTRL_TYPE_DPROXYN, MEMORY_CTRL_TYPE_PROXY, MEMORY_CTRL_TYPE_PROXYN, MEMORY_CTRL_TYPE_SPROXY, MEMORY_CTRL_TYPE_SPROXYN, DesignFlowStep::parameters, and FunctionalUnitStep::TM.

Referenced by Exec().

|

overridevirtual |

Return the name of this design step.

Implements DesignFlowStep.

Definition at line 734 of file RTL_characterization.cpp.

|

overridevirtual |

Return a unified identifier of this design step.

Implements DesignFlowStep.

Definition at line 729 of file RTL_characterization.cpp.

|

overridevirtual |

Check if this step has actually to be executed.

Implements DesignFlowStep.

Definition at line 724 of file RTL_characterization.cpp.

|

overridevirtual |

Initialize the step (i.e., like a constructor, but executed just before exec.

Reimplemented from FunctionalUnitStep.

Definition at line 100 of file RTL_characterization.cpp.

References component, technology_manager::get_library(), technology_manager::get_library_manager(), FunctionalUnitStep::Initialize(), LM, prev_area_characterization, prev_timing_characterization, and FunctionalUnitStep::TM.

|

private |

resize the port w.r.t a given precision

| port |

Definition at line 529 of file RTL_characterization.cpp.

References structural_type_descriptor::BOOL, structural_object::get_typeRef(), port_o::resize_std_port(), structural_type_descriptor::type, structural_type_descriptor::VECTOR_INT, structural_type_descriptor::VECTOR_REAL, and structural_type_descriptor::VECTOR_UINT.

Referenced by AnalyzeCell(), and specialize_fu().

|

private |

Performing the specialization of the given object.

Definition at line 573 of file RTL_characterization.cpp.

References module::get_in_port(), module::get_in_port_size(), structural_object::get_kind(), module::get_out_port(), module::get_out_port_size(), port_vector_o_K, port_o::resize_if_busport(), and resize_port().

Referenced by AnalyzeCell().

|

private |

Add the characterization to the output file.

set to the default value

Definition at line 382 of file RTL_characterization.cpp.

References xml_child::add_child_element(), xml_child::add_child_text(), cells, completed, area_info::factory(), GET_CLASS_NAME, library_manager::get_library_fu(), library_manager::get_library_name(), TimeStamp::GetCurrentTimeStamp(), LM, DesignFlowStep::parameters, STR, THROW_ERROR, and WRITE_XNVM2.

Referenced by xwrite_device_file().

|

private |

Generate the output file.

Definition at line 350 of file RTL_characterization.cpp.

References xml_document::create_root_node(), FunctionalUnitStep::device, GetPath(), THROW_ERROR, xml_document::write_to_file_formatted(), and xwrite_characterization().

Referenced by Exec().

|

private |

The cells to be characterized.

Definition at line 81 of file RTL_characterization.hpp.

Referenced by AnalyzeCell(), and xwrite_characterization().

|

private |

set of units completed with success

Definition at line 122 of file RTL_characterization.hpp.

Referenced by AnalyzeCell(), fix_execution_time_std(), fix_proxies_execution_time_std(), and xwrite_characterization().

|

private |

The component to be characterized.

Definition at line 78 of file RTL_characterization.hpp.

Referenced by ComputeCells(), Exec(), fix_execution_time_std(), fix_proxies_execution_time_std(), and Initialize().

|

private |

True if we are performing dummy synthesis.

Definition at line 91 of file RTL_characterization.hpp.

Referenced by AnalyzeCell().

|

private |

Library manager.

Definition at line 75 of file RTL_characterization.hpp.

Referenced by AnalyzeCell(), Exec(), fix_execution_time_std(), fix_proxies_execution_time_std(), Initialize(), and xwrite_characterization().

|

private |

The area model of the last characterization.

Definition at line 84 of file RTL_characterization.hpp.

Referenced by AnalyzeCell(), and Initialize().

|

private |

The time model of the last characterization.

Definition at line 87 of file RTL_characterization.hpp.

Referenced by AnalyzeCell(), and Initialize().

1.8.13

1.8.13