|

PandA-2024.02

|

|

PandA-2024.02

|

#include <HDL_manager.hpp>

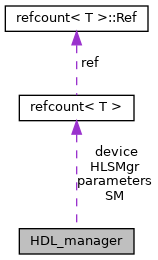

Public Member Functions | |

| HDL_manager (const HLS_managerRef _HLSMgr, const generic_deviceRef device, const ParameterConstRef parameters) | |

| Constructor. More... | |

| HDL_manager (const HLS_managerRef HLSMgr, const generic_deviceRef device, const structural_managerRef SM, const ParameterConstRef parameters) | |

| Constructor. More... | |

| ~HDL_manager () | |

| Destructor. More... | |

| void | hdl_gen (const std::string &filename, const std::list< structural_objectRef > &cirs, std::list< std::string > &hdl_files, std::list< std::string > &aux_files, bool tb) |

| Generates HDL code. More... | |

Static Public Member Functions | |

| static std::string | convert_to_identifier (const language_writer *writer, const std::string &id) |

| Converts a generic string to a language compliant identifier. More... | |

| static std::string | get_mod_typename (const language_writer *lan, const structural_objectRef &cir) |

| Returns the module typename taking into account even the flopoco customizations. More... | |

Private Member Functions | |

| void | get_post_order_structural_components (const structural_objectRef cir, std::list< structural_objectRef > &list_of_com) const |

| Returns the list of components that have a structural-based description. More... | |

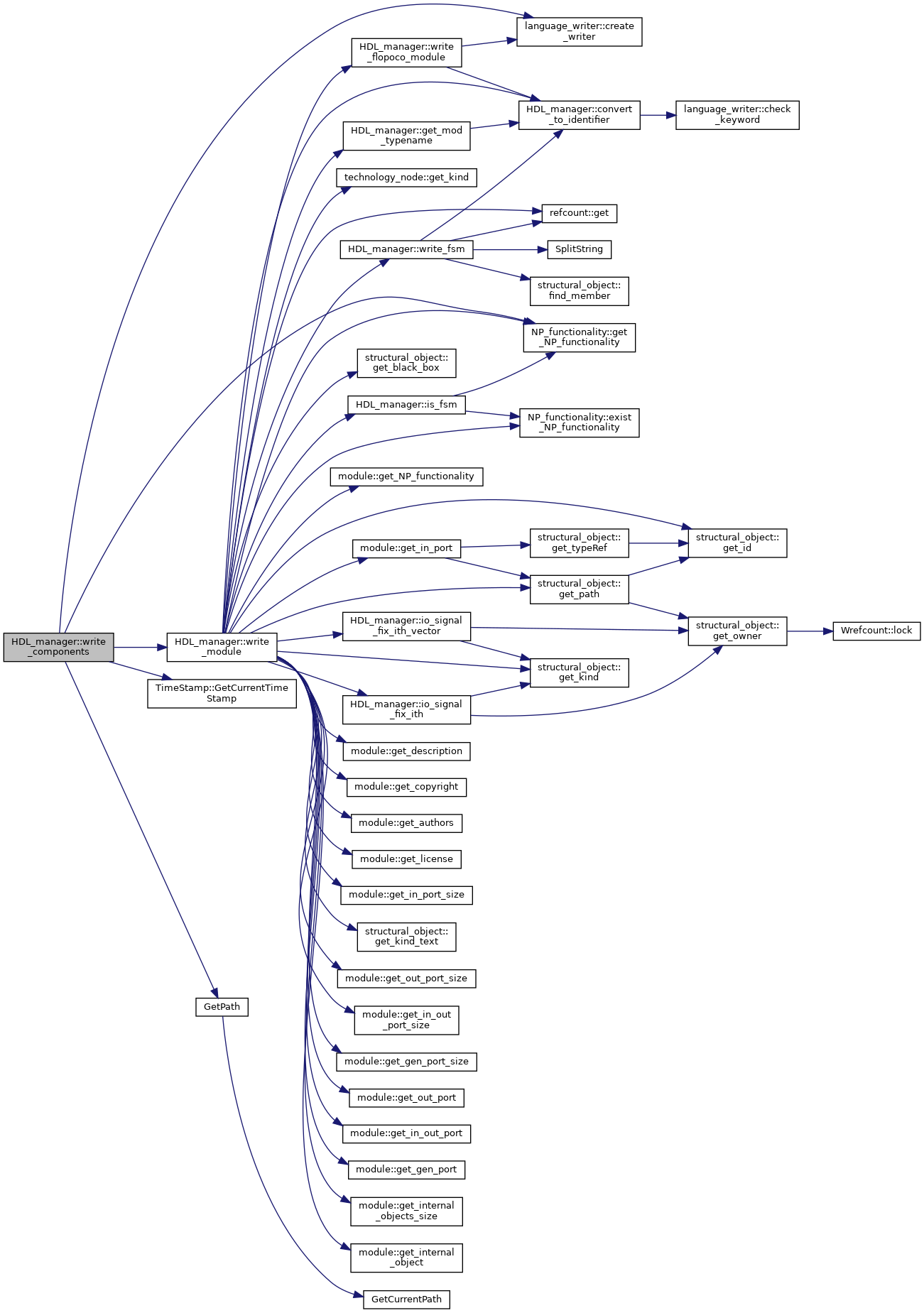

| std::string | write_components (const std::string &filename, const HDLWriter_Language language, const std::list< structural_objectRef > &components, std::list< std::string > &aux_files) const |

| Generates the HDL description for the given components in the specified language. More... | |

| void | write_components (const std::string &filename, const std::list< structural_objectRef > &components, std::list< std::string > &hdl_files, std::list< std::string > &aux_files, bool tb) |

| Determines the proper language for each component and generates the corresponding HDL descriptions. More... | |

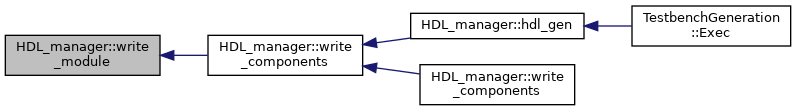

| void | write_module (const language_writerRef writer, const structural_objectRef cir, std::list< std::string > &aux_files) const |

| Writes the module description. More... | |

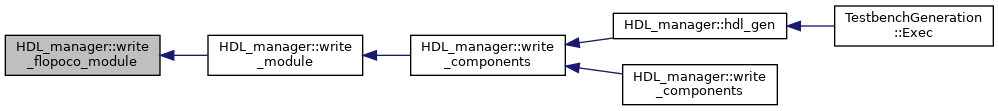

| void | write_flopoco_module (const structural_objectRef &cir, std::list< std::string > &aux_files) const |

| Writes the FloPoCo module description to a VHDL file. More... | |

| void | io_signal_fix_ith (const language_writerRef writer, const structural_objectRef po, bool &lspf) const |

| Writes signal port connection post fix. More... | |

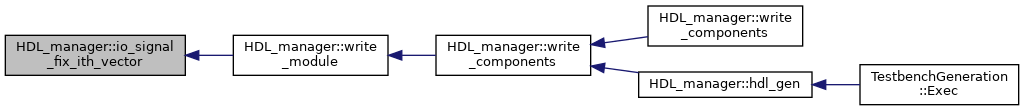

| void | io_signal_fix_ith_vector (const language_writerRef writer, const structural_objectRef po, bool &lspf) const |

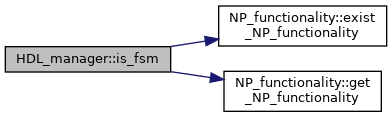

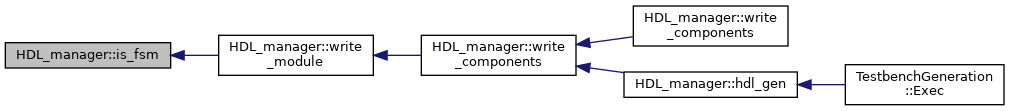

| bool | is_fsm (const structural_objectRef &cir) const |

| Returns true if the module has a FSM description associated with, false otherwise. More... | |

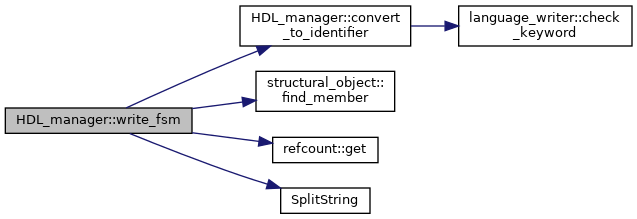

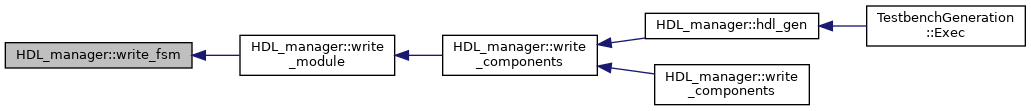

| void | write_fsm (const language_writerRef writer, const structural_objectRef &cir, const std::string &fsm_desc) const |

| Writes a mealy/moore finite state machine behavioral description. More... | |

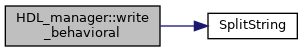

| void | write_behavioral (const language_writerRef writer, const structural_objectRef &cir, const std::string &behav) const |

| Writes the behavioral description associated with the component. More... | |

Private Attributes | |

| const HLS_managerRef | HLSMgr |

| The high level synthesis manager. More... | |

| const generic_deviceRef | device |

| reference to the target device More... | |

| const technology_managerConstRef | TM |

| reference to the class containing all the technology information More... | |

| const structural_managerRef | SM |

| The structural manager containing top. More... | |

| const ParameterConstRef | parameters |

| The set of input parameters. More... | |

| const int | debug_level |

| The debug level. More... | |

Definition at line 77 of file HDL_manager.hpp.

| HDL_manager::HDL_manager | ( | const HLS_managerRef | _HLSMgr, |

| const generic_deviceRef | device, | ||

| const ParameterConstRef | parameters | ||

| ) |

Constructor.

| hls_manager | is the high level synthesis manager |

| device | is the data structure containing information about the target device |

| parameters | is the data structure containing all the parameters |

Definition at line 113 of file HDL_manager.cpp.

References ~HDL_manager().

| HDL_manager::HDL_manager | ( | const HLS_managerRef | _HLSMgr, |

| const generic_deviceRef | _device, | ||

| const structural_managerRef | _SM, | ||

| const ParameterConstRef | _parameters | ||

| ) |

Constructor.

Header include.

| HLS | is the high level synthesis manager |

| device | is the data structure containing information about the target device |

| SM | is the structural manager containing the top component |

| parameters | is the data structure containing all the parameters |

Autoheader include boost include design_flows include design_flows/backend/ToHDL includes HLS include STL include technology includes

Definition at line 98 of file HDL_manager.cpp.

|

default |

|

static |

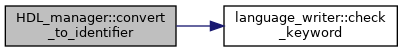

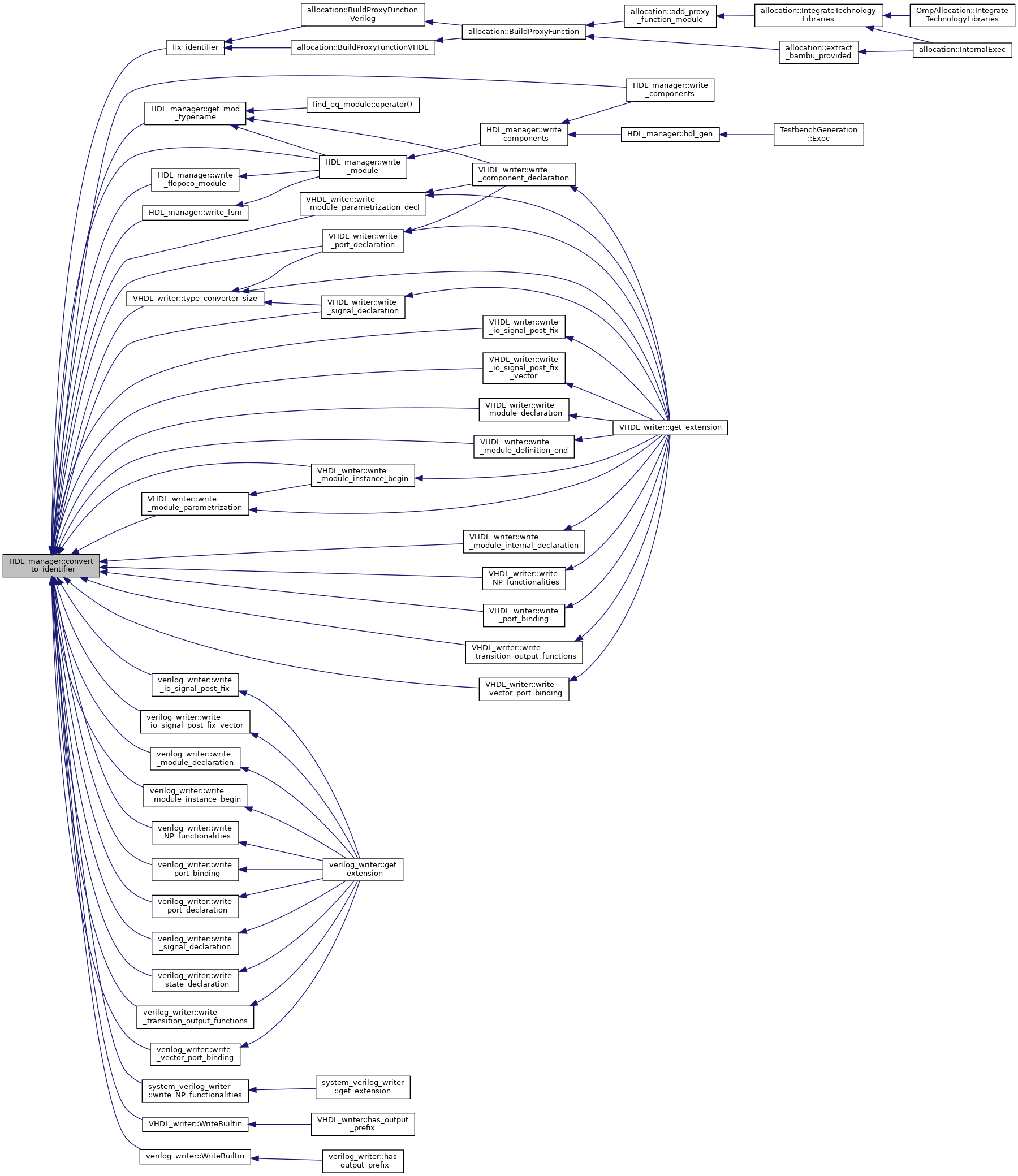

Converts a generic string to a language compliant identifier.

Definition at line 1323 of file HDL_manager.cpp.

References language_writer::check_keyword(), and THROW_UNREACHABLE.

Referenced by fix_identifier(), get_mod_typename(), VHDL_writer::type_converter_size(), write_components(), write_flopoco_module(), write_fsm(), VHDL_writer::write_io_signal_post_fix(), verilog_writer::write_io_signal_post_fix(), VHDL_writer::write_io_signal_post_fix_vector(), verilog_writer::write_io_signal_post_fix_vector(), write_module(), VHDL_writer::write_module_declaration(), verilog_writer::write_module_declaration(), VHDL_writer::write_module_definition_end(), VHDL_writer::write_module_instance_begin(), verilog_writer::write_module_instance_begin(), VHDL_writer::write_module_internal_declaration(), VHDL_writer::write_module_parametrization(), VHDL_writer::write_module_parametrization_decl(), system_verilog_writer::write_NP_functionalities(), VHDL_writer::write_NP_functionalities(), verilog_writer::write_NP_functionalities(), VHDL_writer::write_port_binding(), verilog_writer::write_port_binding(), verilog_writer::write_port_declaration(), VHDL_writer::write_port_declaration(), verilog_writer::write_signal_declaration(), VHDL_writer::write_signal_declaration(), verilog_writer::write_state_declaration(), VHDL_writer::write_transition_output_functions(), verilog_writer::write_transition_output_functions(), VHDL_writer::write_vector_port_binding(), verilog_writer::write_vector_port_binding(), VHDL_writer::WriteBuiltin(), and verilog_writer::WriteBuiltin().

|

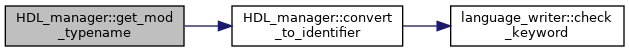

static |

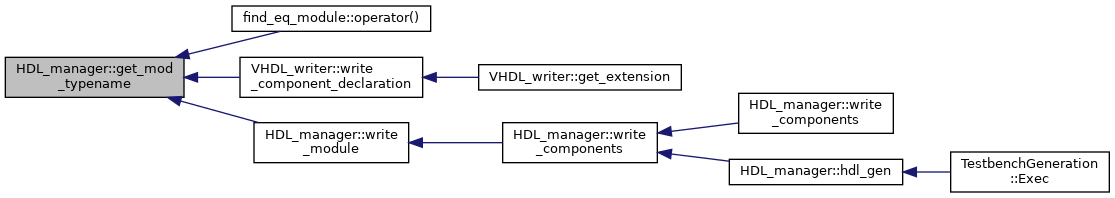

Returns the module typename taking into account even the flopoco customizations.

| lan | is the chosen language writer object. |

| cir | is the module. |

Definition at line 1365 of file HDL_manager.cpp.

References convert_to_identifier(), NP_functionality::FLOPOCO_PROVIDED, GET_TYPE_NAME, lenet_tvm::mod, PIPE_PARAMETER, STD_GET_SIZE, and STR.

Referenced by find_eq_module::operator()(), VHDL_writer::write_component_declaration(), and write_module().

|

private |

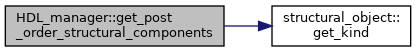

Returns the list of components that have a structural-based description.

This list of components is relative sorted such that if a component C_i uses a component C_j then C_j is before C_i. To obtain this list the hierarchy is visited in a post-order fashion.

| lan | is the chosen language writer object. |

| cir | is the structural object under analysis. |

| list_of_com | is the list of components. |

no action for signals and bus

Definition at line 481 of file HDL_manager.cpp.

References action_o_K, bus_connection_o_K, channel_o_K, component_o_K, constant_o_K, data_o_K, event_o_K, functional_unit_K, functional_unit_template_K, structural_object::get_kind(), GET_TYPE_NAME, NP_functionality::IP_COMPONENT, lenet_tvm::mod, port_o_K, port_vector_o_K, signal_o_K, signal_vector_o_K, THROW_ASSERT, THROW_ERROR, and TM.

Referenced by hdl_gen().

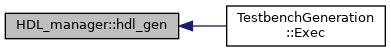

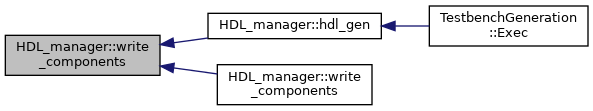

| void HDL_manager::hdl_gen | ( | const std::string & | filename, |

| const std::list< structural_objectRef > & | cirs, | ||

| std::list< std::string > & | hdl_files, | ||

| std::list< std::string > & | aux_files, | ||

| bool | tb | ||

| ) |

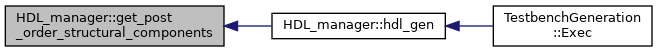

Generates HDL code.

| file_name | is the name to be created |

| cirs | are the structural objects representing the components to be generated |

| the | created files (file_name + other files) |

| the | created aux files |

compute the list of components for which a structural description exist.

generate the HDL descriptions for all the components

Definition at line 420 of file HDL_manager.cpp.

References debug_level, DEBUG_LEVEL_VERY_PEDANTIC, get_post_order_structural_components(), PRINT_DBG_MEX, THROW_ASSERT, and write_components().

Referenced by TestbenchGeneration::Exec().

|

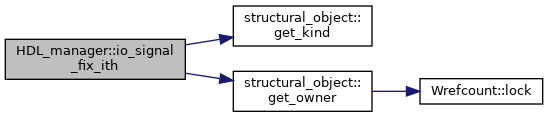

private |

Writes signal port connection post fix.

| lan | is the chosen language writer object. |

| po | is the primary port. |

| lspf | is true when the first post is written |

Definition at line 588 of file HDL_manager.cpp.

References constant_o_K, structural_object::get_kind(), structural_object::get_owner(), port_o_K, port_vector_o_K, signal_o_K, signal_vector_o_K, and THROW_ASSERT.

Referenced by write_module().

|

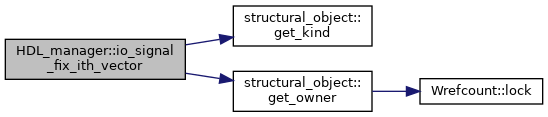

private |

Definition at line 623 of file HDL_manager.cpp.

References constant_o_K, structural_object::get_kind(), structural_object::get_owner(), port_vector_o_K, signal_vector_o_K, THROW_ASSERT, and THROW_ERROR.

Referenced by write_module().

|

private |

Returns true if the module has a FSM description associated with, false otherwise.

| cir | is the module. |

check for a FSM description

Definition at line 467 of file HDL_manager.cpp.

References NP_functionality::exist_NP_functionality(), NP_functionality::FSM, NP_functionality::FSM_CS, NP_functionality::get_NP_functionality(), and THROW_ASSERT.

Referenced by write_module().

|

private |

Writes the behavioral description associated with the component.

| writer | is the chosen language writer object. |

| cir | is the module. |

| behav | is the string-based behavioral description. |

Definition at line 1168 of file HDL_manager.cpp.

References SplitString(), and THROW_ASSERT.

|

private |

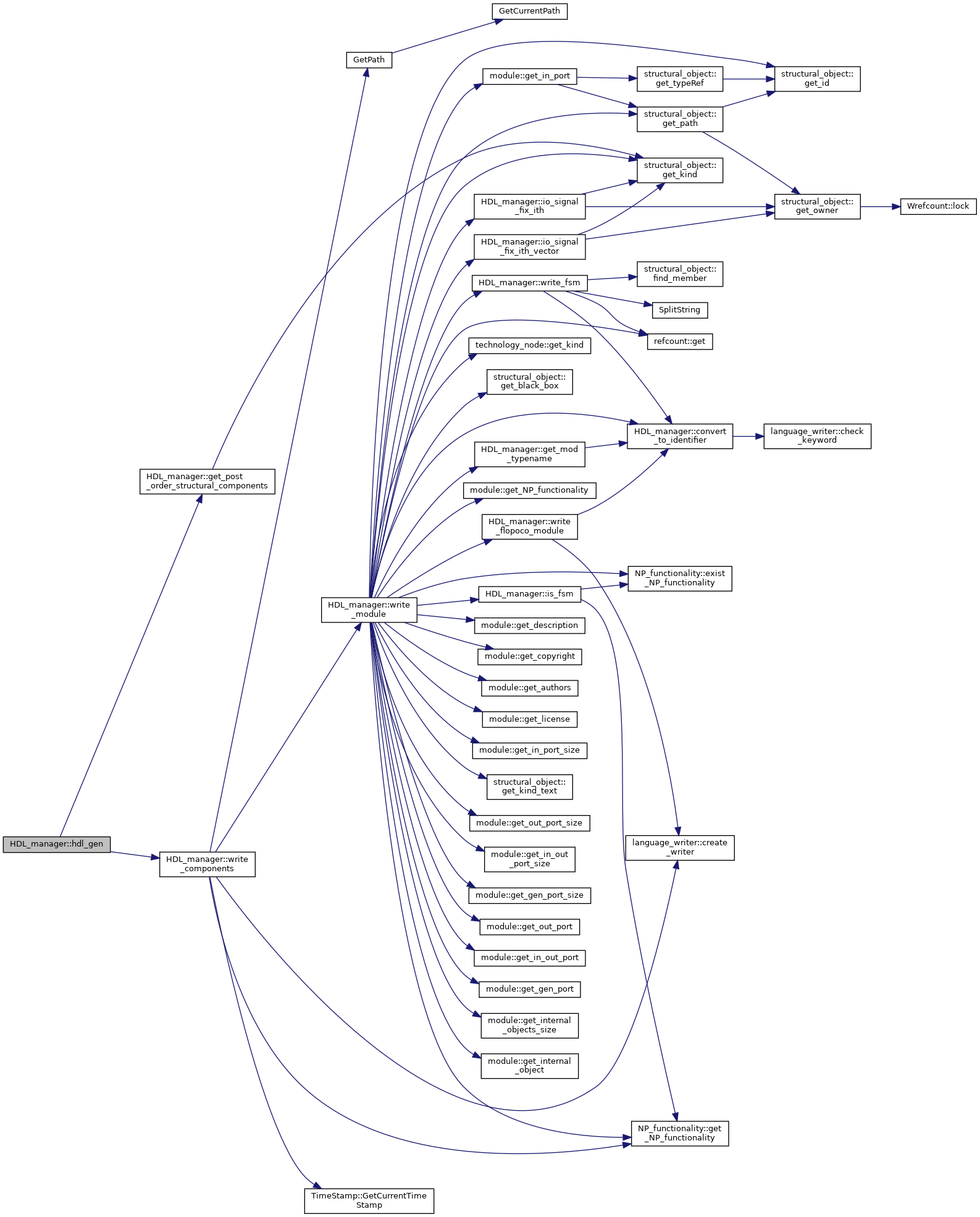

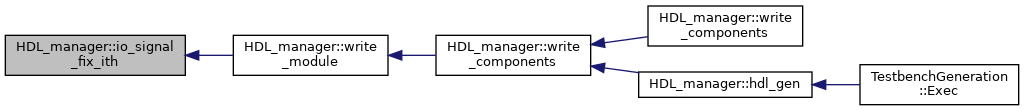

Generates the HDL description for the given components in the specified language.

write the header of the file

write all modules

we write the definition of the object stored in library

Definition at line 129 of file HDL_manager.cpp.

References language_writer::create_writer(), debug_level, DEBUG_LEVEL_VERY_PEDANTIC, NP_functionality::FLOPOCO_PROVIDED, NP_functionality::get_NP_functionality(), TimeStamp::GetCurrentTimeStamp(), GetPath(), INDENT_DBG_MEX, parameters, THROW_ASSERT, THROW_ERROR, THROW_UNREACHABLE, TM, VERILOG, NP_functionality::VERILOG_FILE_PROVIDED, VHDL, NP_functionality::VHDL_FILE_PROVIDED, and write_module().

Referenced by hdl_gen(), and write_components().

|

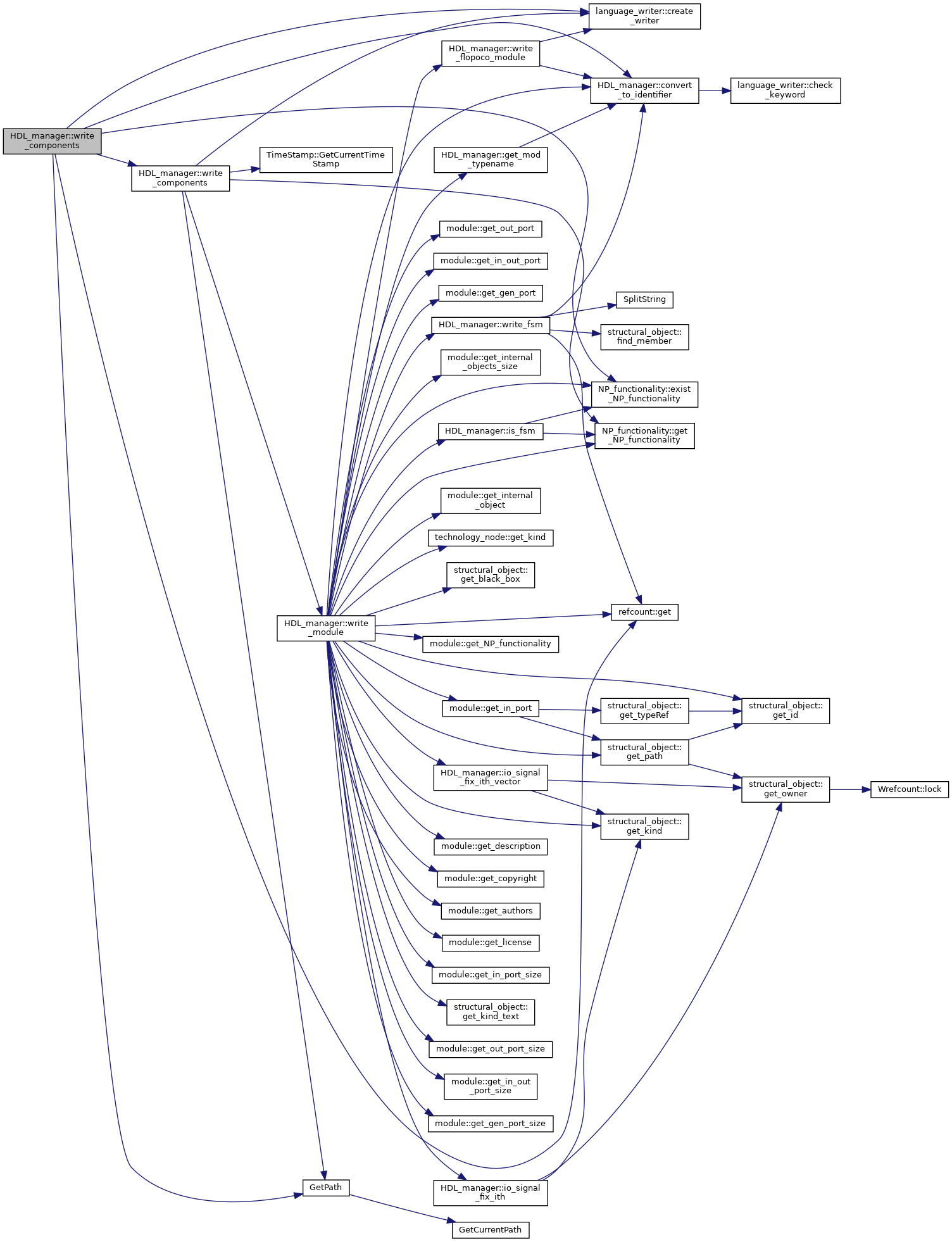

private |

Determines the proper language for each component and generates the corresponding HDL descriptions.

default language

determine the proper language for each component

generate the auxiliary files

add the generated file to the global list

Definition at line 237 of file HDL_manager.cpp.

References convert_to_identifier(), counter, language_writer::create_writer(), debug_level, DEBUG_LEVEL_VERY_PEDANTIC, NP_functionality::exist_NP_functionality(), flopoco::filename, NP_functionality::FLOPOCO_PROVIDED, NP_functionality::FSM, NP_functionality::FSM_CS, refcount< T >::get(), GET_TYPE_NAME, GetPath(), lenet_tvm::mod, parameters, PRINT_DBG_MEX, SYSTEM_VERILOG, NP_functionality::SYSTEM_VERILOG_PROVIDED, THROW_ASSERT, THROW_ERROR, THROW_WARNING, TM, test_panda::type, NP_functionality::UNKNOWN, VERILOG, NP_functionality::VERILOG_FILE_PROVIDED, NP_functionality::VERILOG_PROVIDED, VHDL, NP_functionality::VHDL_FILE_PROVIDED, NP_functionality::VHDL_PROVIDED, and write_components().

|

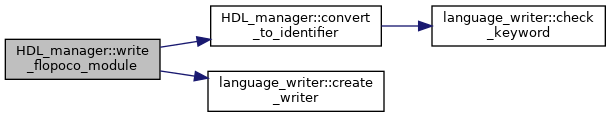

private |

Writes the FloPoCo module description to a VHDL file.

| cir | is the module to be fixed. |

Definition at line 1120 of file HDL_manager.cpp.

References convert_to_identifier(), language_writer::create_writer(), debug_level, DEBUG_LEVEL_PEDANTIC, NP_functionality::FLOPOCO_PROVIDED, GET_TYPE_NAME, parameters, PIPE_PARAMETER, PRINT_DBG_MEX, STD_GET_SIZE, STR, THROW_ERROR, TM, and VHDL.

Referenced by write_module().

|

private |

Writes a mealy/moore finite state machine behavioral description.

| writer | is the chosen language writer object. |

| cir | is the module. |

| fsm_desc | is the string-based FSM description. |

extract bypass signals

write state declaration.

write the present_state update

write transition and output functions

Definition at line 1182 of file HDL_manager.cpp.

References convert_to_identifier(), debug_level, DEBUG_LEVEL_VERBOSE, device, structural_object::find_member(), refcount< T >::get(), lenet_tvm::mod, NEXT_STATE_PORT_NAME, parameters, port_o_K, PRESENT_STATE_PORT_NAME, PRINT_DBG_MEX, SplitString(), STR, THROW_ASSERT, and test_panda::tokens.

Referenced by write_module().

|

private |

Writes the module description.

| lan | is the chosen language writer object. |

| cir | is the module to be written. The analysis does not consider the inner objects but just one level of the hierarchy. |

write module declaration

write library declaration component

write IO port declarations

close the interface declaration and start the implementation

write components declarations write signal declarations

write module_instantiation begin

write module instantiation & connection binding

write IO ports binding

First output and then input. Some backend could have benefits from this ordering. Some customization are possible, like direct translation of gates into built-in statements.

write loop signal post fix

for generic ports the post fix is not required. A generic port is never attached to a signal.

check if there is some behavior attached to the module

write module_instantiation end

Definition at line 648 of file HDL_manager.cpp.

References action_o_K, bus_connection_o_K, channel_o_K, component_o_K, constant_o_K, convert_to_identifier(), data_o_K, debug_level, DEBUG_LEVEL_PARANOIC, DEBUG_LEVEL_VERY_PEDANTIC, event_o_K, NP_functionality::exist_NP_functionality(), NP_functionality::FLOPOCO_PROVIDED, NP_functionality::FSM, NP_functionality::FSM_CS, functional_unit_K, functional_unit_template_K, refcount< T >::get(), module::get_authors(), structural_object::get_black_box(), module::get_copyright(), module::get_description(), module::get_gen_port(), module::get_gen_port_size(), structural_object::get_id(), module::get_in_out_port(), module::get_in_out_port_size(), module::get_in_port(), module::get_in_port_size(), module::get_internal_object(), module::get_internal_objects_size(), technology_node::get_kind(), structural_object::get_kind(), structural_object::get_kind_text(), module::get_license(), get_mod_typename(), NP_functionality::get_NP_functionality(), module::get_NP_functionality(), module::get_out_port(), module::get_out_port_size(), structural_object::get_path(), GET_TYPE_NAME, INDENT_DBG_MEX, io_signal_fix_ith(), io_signal_fix_ith_vector(), NP_functionality::IP_COMPONENT, is_fsm(), k, lenet_tvm::mod, port_o_K, port_vector_o_K, PRINT_DBG_MEX, signal_o_K, signal_vector_o_K, THROW_ASSERT, THROW_ERROR, TM, write_flopoco_module(), and write_fsm().

Referenced by write_components().

|

private |

The debug level.

Definition at line 101 of file HDL_manager.hpp.

Referenced by hdl_gen(), write_components(), write_flopoco_module(), write_fsm(), and write_module().

|

private |

reference to the target device

Definition at line 84 of file HDL_manager.hpp.

Referenced by write_fsm().

|

private |

The high level synthesis manager.

Definition at line 81 of file HDL_manager.hpp.

|

private |

The set of input parameters.

Definition at line 98 of file HDL_manager.hpp.

Referenced by write_components(), write_flopoco_module(), and write_fsm().

|

private |

The structural manager containing top.

Definition at line 95 of file HDL_manager.hpp.

|

private |

reference to the class containing all the technology information

Definition at line 87 of file HDL_manager.hpp.

Referenced by get_post_order_structural_components(), write_components(), write_flopoco_module(), and write_module().

1.8.13

1.8.13