|

PandA-2024.02

|

|

PandA-2024.02

|

#include <testbench_generation.hpp>

Public Member Functions | |

| TestbenchGeneration (const ParameterConstRef parameters, const HLS_managerRef _HLSMgr, const DesignFlowManagerConstRef design_flow_manager) | |

| Constructor. More... | |

| void | Initialize () override |

| Initialize the step (i.e., like a constructor, but executed just before exec. More... | |

| bool | HasToBeExecuted () const override |

| Check if this step has actually to be executed. More... | |

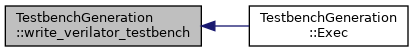

| DesignFlowStep_Status | Exec () override |

| Execute the step. More... | |

Public Member Functions inherited from HLS_step Public Member Functions inherited from HLS_step | |

| HLS_step (const ParameterConstRef _parameters, const HLS_managerRef HLSMgr, const DesignFlowManagerConstRef design_flow_manager, const HLSFlowStep_Type hls_flow_step_type, const HLSFlowStepSpecializationConstRef hls_flow_step_specialization=HLSFlowStepSpecializationConstRef()) | |

| Constructor. More... | |

| ~HLS_step () override | |

| Destructor. More... | |

| std::string | GetSignature () const override |

| Return a unified identifier of this design step. More... | |

| std::string | GetName () const override |

| Return the name of this design step. More... | |

| virtual std::string | GetKindText () const |

| Return the name of the type of this frontend flow step. More... | |

| DesignFlowStepFactoryConstRef | CGetDesignFlowStepFactory () const final |

| Return the factory to create this type of steps. More... | |

Public Member Functions inherited from DesignFlowStep Public Member Functions inherited from DesignFlowStep | |

| DesignFlowStep (const DesignFlowManagerConstRef design_flow_manager, const ParameterConstRef parameters) | |

| Constructor. More... | |

| virtual | ~DesignFlowStep () |

| Destructor. More... | |

| DesignFlowStep_Status | GetStatus () const |

| Return the status of this design step. More... | |

| virtual void | WriteDot (std::ostream &out) const |

| Write the label for a dot graph. More... | |

| bool | IsComposed () const |

| Returns if this step is composed. More... | |

| int | CGetDebugLevel () const |

| Return the debug level of the step. More... | |

| virtual void | PrintInitialIR () const |

| Dump the initial intermediate representation. More... | |

| virtual void | PrintFinalIR () const |

| Dump the final intermediate representation. More... | |

Static Public Member Functions | |

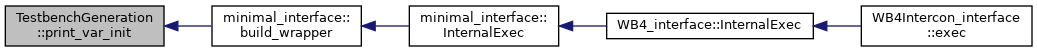

| static std::vector< std::string > | print_var_init (const tree_managerConstRef TreeM, unsigned int var, const memoryRef mem) |

| static unsigned long long | generate_init_file (const std::string &dat_filename, const tree_managerConstRef TreeM, unsigned int var, const memoryRef mem) |

Static Public Member Functions inherited from HLS_step Static Public Member Functions inherited from HLS_step | |

| static std::string | EnumToName (const HLSFlowStep_Type hls_flow_step_type) |

| Given a HLS flow step type, return the name of the type. More... | |

| static const std::string | ComputeSignature (const HLSFlowStep_Type hls_flow_step_type, const HLSFlowStepSpecializationConstRef hls_flow_step_specialization) |

| Compute the signature of a hls flow step. More... | |

Private Member Functions | |

| bool | printCacheStats (const module *rootMod) const |

| This function takes care of printing cache hit/miss counters. More... | |

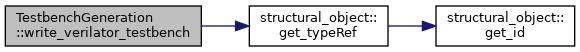

| std::string | write_verilator_testbench () const |

| Write the verilator testbench. More... | |

| const CustomUnorderedSet< std::tuple< HLSFlowStep_Type, HLSFlowStepSpecializationConstRef, HLSFlowStep_Relationship > > | ComputeHLSRelationships (const DesignFlowStep::RelationshipType relationship_type) const override |

| Return the set of analyses in relationship with this design step. More... | |

| void | ComputeRelationships (DesignFlowStepSet &design_flow_step_set, const DesignFlowStep::RelationshipType relationship_type) override |

| Compute the relationships of a step with other steps. More... | |

Private Attributes | |

| const language_writerRef | writer |

| structural_objectRef | cir |

| const module * | mod |

| const std::string | output_directory |

| output directory More... | |

| const std::string | c_testbench_basename |

| std::string | hdl_testbench_basename |

| testbench basename More... | |

Additional Inherited Members | |

Public Types inherited from DesignFlowStep Public Types inherited from DesignFlowStep | |

| enum | RelationshipType { DEPENDENCE_RELATIONSHIP, INVALIDATION_RELATIONSHIP, PRECEDENCE_RELATIONSHIP } |

| The relationship type. More... | |

Protected Attributes inherited from HLS_step Protected Attributes inherited from HLS_step | |

| const HLS_managerRef | HLSMgr |

| information about all the HLS synthesis More... | |

| const HLSFlowStep_Type | hls_flow_step_type |

| The type of this step. More... | |

| const HLSFlowStepSpecializationConstRef | hls_flow_step_specialization |

| The information about specialization. More... | |

Protected Attributes inherited from DesignFlowStep Protected Attributes inherited from DesignFlowStep | |

| bool | composed |

| True if this step represents a composition of design flow steps (e.g., a flow); must be set by specialized constructors. More... | |

| const Wrefcount< const DesignFlowManager > | design_flow_manager |

| The design flow manager. More... | |

| const ParameterConstRef | parameters |

| Set of input parameters. More... | |

| int | debug_level |

| The debug level. More... | |

| const int | output_level |

| The output level. More... | |

Static Protected Attributes inherited from HLS_step Static Protected Attributes inherited from HLS_step | |

| static CustomUnorderedMap< std::string, HLSFlowStep_Type > | command_line_name_to_enum |

| Map hls step name to enum. More... | |

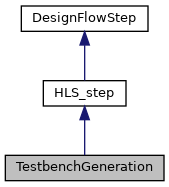

Definition at line 64 of file testbench_generation.hpp.

| TestbenchGeneration::TestbenchGeneration | ( | const ParameterConstRef | parameters, |

| const HLS_managerRef | _HLSMgr, | ||

| const DesignFlowManagerConstRef | design_flow_manager | ||

| ) |

Constructor.

| parameters | is the set of input parameters |

| hls_mgr | is the HLS manager |

| design_flow_manager | is the design flow manager |

Definition at line 91 of file testbench_generation.cpp.

References DesignFlowStep::debug_level, GET_CLASS, DesignFlowStep::parameters, TESTBENCH_GENERATION, and VERILOG.

|

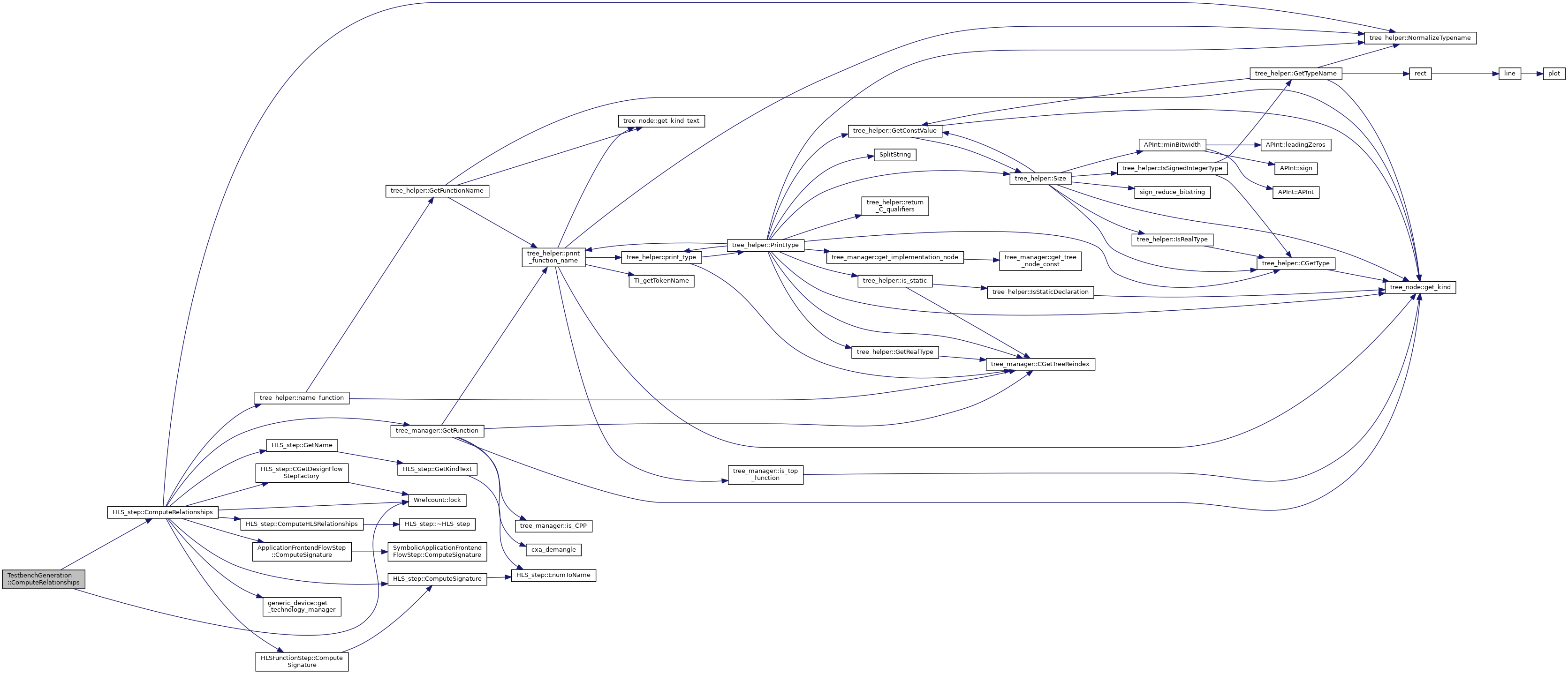

overrideprivatevirtual |

Return the set of analyses in relationship with this design step.

| relationship_type | is the type of relationship to be considered |

Reimplemented from HLS_step.

Definition at line 105 of file testbench_generation.cpp.

References DesignFlowStep::DEPENDENCE_RELATIONSHIP, DesignFlowStep::INVALIDATION_RELATIONSHIP, DesignFlowStep::parameters, DesignFlowStep::PRECEDENCE_RELATIONSHIP, TEST_VECTOR_PARSER, THROW_UNREACHABLE, and TOP_FUNCTION.

|

overrideprivatevirtual |

Compute the relationships of a step with other steps.

| dependencies | is where relationships will be stored |

| relationship_type | is the type of relationship to be computed |

check if __builtin_memcpy has to be synthesized

FIXME: temporary deactivated

Managed in HLSFunctionStep::ComputeRelationships

Root function cannot be computed at the beginning

Reimplemented from HLS_step.

Definition at line 135 of file testbench_generation.cpp.

References c_testbench_basename, HLS_step::ComputeRelationships(), DesignFlowStep::DEPENDENCE_RELATIONSHIP, DesignFlowStep::design_flow_manager, DesignFlowStep::INVALIDATION_RELATIONSHIP, Wrefcount< T >::lock(), output_directory, DesignFlowStep::PRECEDENCE_RELATIONSHIP, and THROW_UNREACHABLE.

|

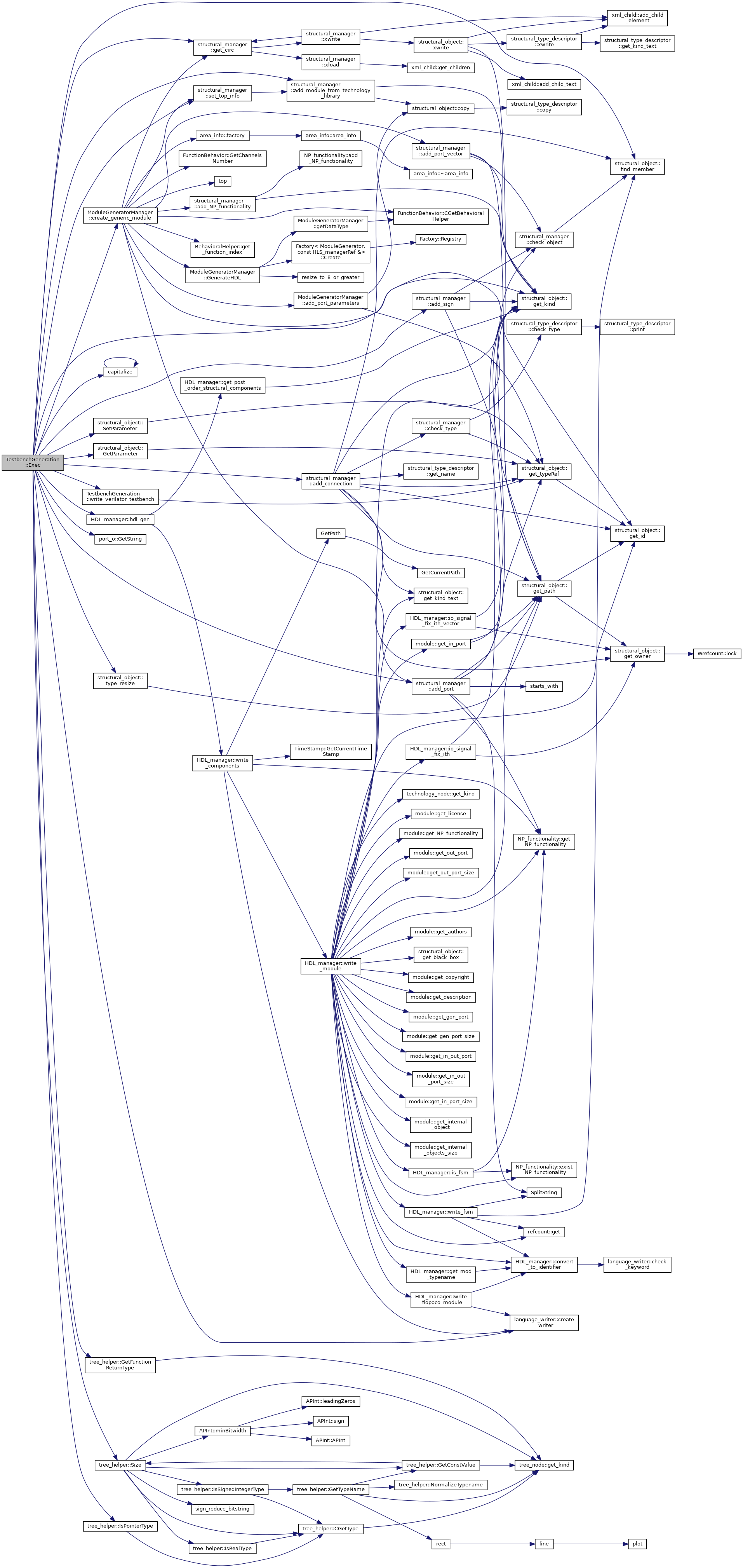

overridevirtual |

Execute the step.

Set some descriptions and legal stuff

command signal type descriptor

add clock port

VCD output generation (optional)

Implements DesignFlowStep.

Definition at line 184 of file testbench_generation.cpp.

References structural_manager::add_connection(), structural_manager::add_module_from_technology_library(), structural_manager::add_port(), structural_manager::add_sign(), AND_GATE_STD, test_panda::arg, capitalize(), CLOCK_PORT_NAME, component_o_K, ModuleGeneratorManager::create_generic_module(), language_writer::create_writer(), CST_STR_BAMBU_TESTBENCH, DesignFlowStep::debug_level, DEBUG_LEVEL_MINIMUM, DONE_PORT_NAME, structural_object::find_member(), GENERATED_COPYRIGHT, GENERATED_LICENSE, structural_manager::get_circ(), GET_INDEX_CONST_NODE, structural_object::get_kind(), tree_helper::GetFunctionReturnType(), structural_object::GetParameter(), port_o::GetString(), HDL_manager::hdl_gen(), HIERARCHY_SEPARATOR, HLS_step::HLSMgr, INDENT_DBG_MEX, INFERRED_INTERFACE_GENERATION, INTERFACE_CS_GENERATION, tree_helper::IsPointerType(), k, LIBRARY_STD, MINIMAL_INTERFACE_GENERATION, MOUT_BACK_PRESSURE_PORT_NAME, MOUT_OE_PORT_NAME, OR_GATE_STD, output_directory, OUTPUT_LEVEL_VERY_PEDANTIC, DesignFlowStep::parameters, port_o_K, RESET_PORT_NAME, RETURN_PORT_NAME, structural_manager::set_top_info(), structural_object::SetParameter(), SETUP_PORT_NAME, signal_o_K, tree_helper::Size(), START_PORT_NAME, STD_CLOSING_CHAR, STD_GET_SIZE, STD_OPENING_CHAR, STR, STR_CST_INIT_TIME, SUCCESS, THROW_ASSERT, THROW_ERROR, THROW_UNREACHABLE, structural_object::type_resize(), U, VERILOG, VHDL, WB4_INTERCON_INTERFACE_GENERATION, WB4_INTERFACE_GENERATION, and write_verilator_testbench().

|

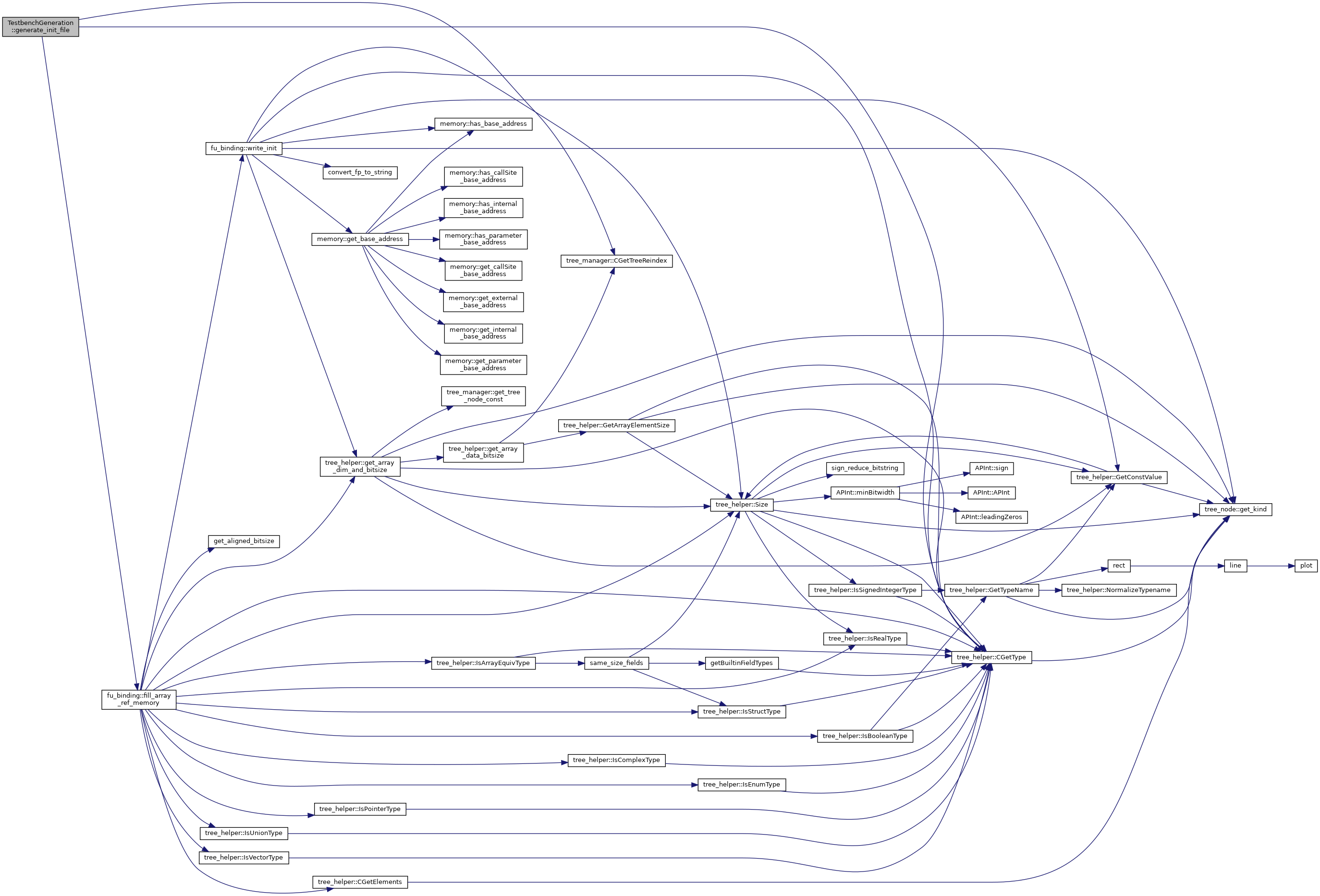

static |

Definition at line 933 of file testbench_generation.cpp.

References tree_manager::CGetTreeReindex(), tree_helper::CGetType(), fu_binding::fill_array_ref_memory(), GET_CONST_NODE, k, THROW_ASSERT, and U.

Referenced by HLSCWriter::WriteSimulatorInitMemory().

|

overridevirtual |

Check if this step has actually to be executed.

Implements DesignFlowStep.

Definition at line 167 of file testbench_generation.cpp.

|

overridevirtual |

Initialize the step (i.e., like a constructor, but executed just before exec.

Reimplemented from DesignFlowStep.

Definition at line 172 of file testbench_generation.cpp.

References cir, structural_object::get_id(), GET_INDEX_CONST_NODE, hdl_testbench_basename, HLS_step::HLSMgr, mod, DesignFlowStep::parameters, and THROW_ASSERT.

|

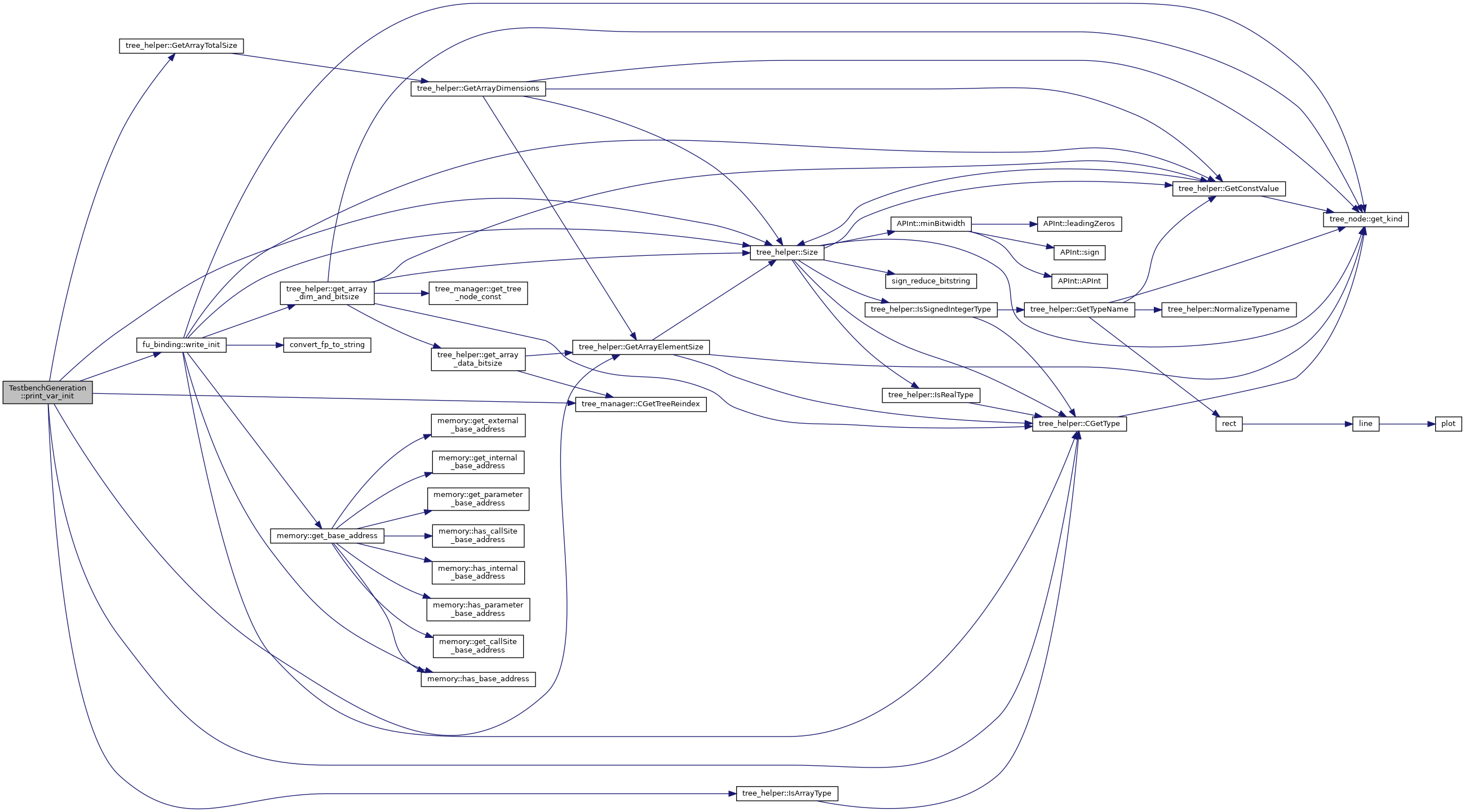

static |

Definition at line 891 of file testbench_generation.cpp.

References tree_manager::CGetTreeReindex(), tree_helper::CGetType(), GET_CONST_NODE, tree_helper::GetArrayElementSize(), tree_helper::GetArrayTotalSize(), tree_helper::IsArrayType(), tree_helper::Size(), test_panda::type, and fu_binding::write_init().

Referenced by minimal_interface::build_wrapper().

This function takes care of printing cache hit/miss counters.

Starting from the root module, it visits all submodules and checks if they have axi ports, then recursively visits axi children. If no axi children are found, the current node is the axi controller and can print the axi cache stats.

| rootMod | Root module the search must be started from. |

|

private |

Write the verilator testbench.

| input_file | Filename of the stimuli file. |

Definition at line 827 of file testbench_generation.cpp.

References CLOCK_PORT_NAME, CST_STR_BAMBU_TESTBENCH, flopoco::filename, structural_object::get_typeRef(), structural_type_descriptor::id_type, mod, and output_directory.

Referenced by Exec().

|

private |

Definition at line 79 of file testbench_generation.hpp.

Referenced by ComputeRelationships().

|

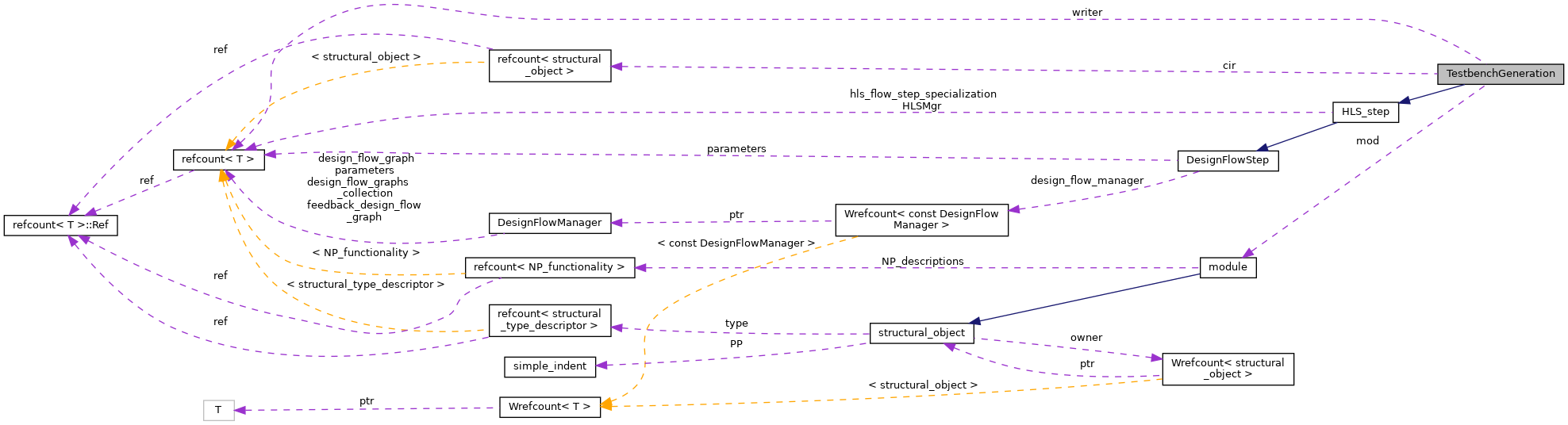

private |

Definition at line 72 of file testbench_generation.hpp.

Referenced by Initialize().

|

private |

testbench basename

Definition at line 82 of file testbench_generation.hpp.

Referenced by Initialize().

|

private |

Definition at line 74 of file testbench_generation.hpp.

Referenced by Initialize(), and write_verilator_testbench().

|

private |

output directory

Definition at line 77 of file testbench_generation.hpp.

Referenced by ComputeRelationships(), Exec(), and write_verilator_testbench().

|

private |

Definition at line 70 of file testbench_generation.hpp.

1.8.13

1.8.13