|

PandA-2024.02

|

|

PandA-2024.02

|

#include <verilog_writer.hpp>

Public Member Functions | |

| std::string | get_name () const override |

| Return the name of the language writer. More... | |

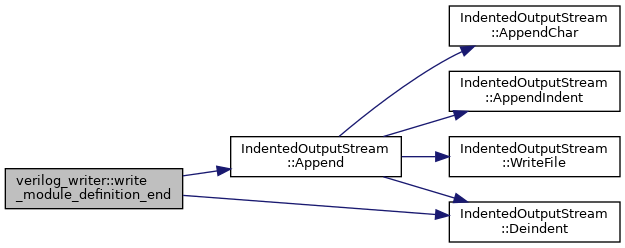

| std::string | get_extension () const override |

| Return the filename extension associated with the verilog_writer. More... | |

| void | write_comment (const std::string &comment_string) override |

| Print a comment. More... | |

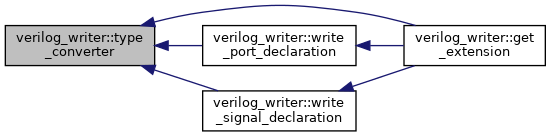

| std::string | type_converter (structural_type_descriptorRef Type) override |

| Return a language based type string given a structural_type_descriptor. More... | |

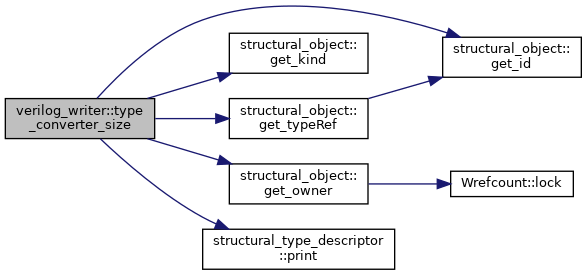

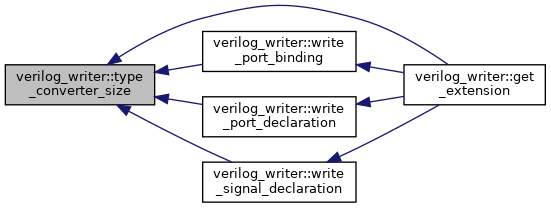

| std::string | type_converter_size (const structural_objectRef &cir) override |

| Return a language based type string given a structural_type_descriptor for the range of the array. More... | |

| std::string | may_slice_string (const structural_objectRef &cir) |

| return the slice in case of a port owned by a port vector More... | |

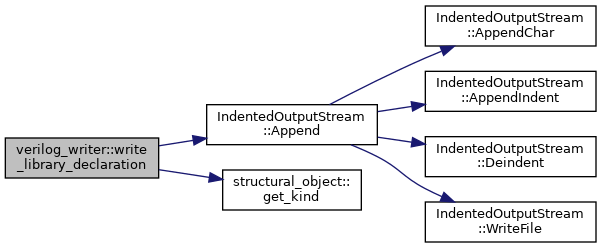

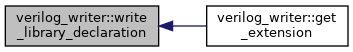

| void | write_library_declaration (const structural_objectRef &cir) override |

| Write the #include for each used library. More... | |

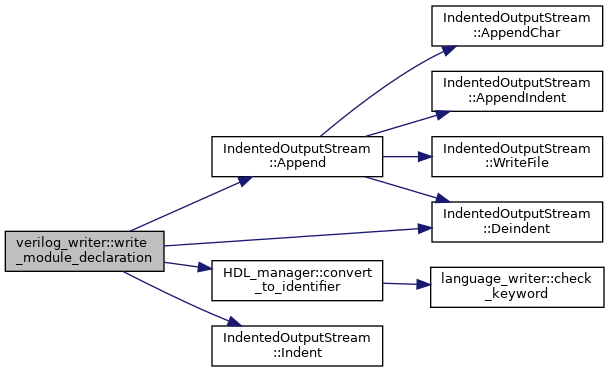

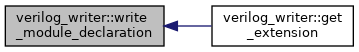

| void | write_module_declaration (const structural_objectRef &cir) override |

| Write the declaration of the module. More... | |

| void | write_module_internal_declaration (const structural_objectRef &cir) override |

| Write the declaration of internal objects of the module. More... | |

| void | write_port_declaration (const structural_objectRef &cir, bool last_port_to_analyze) override |

| Write the port declaration starting from a port object. More... | |

| void | write_component_declaration (const structural_objectRef &cir) override |

| Write the declaration of a component. More... | |

| void | write_signal_declaration (const structural_objectRef &cir) override |

| Write the declaration of a signal. More... | |

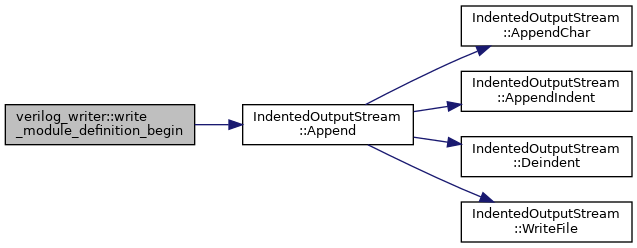

| void | write_module_definition_begin (const structural_objectRef &cir) override |

| Write the top constructor declaration. More... | |

| void | write_module_instance_begin (const structural_objectRef &cir, const std::string &module_name, bool write_parametrization) override |

| Write the initial part of the instance of a module. More... | |

| void | write_module_instance_end (const structural_objectRef &cir) override |

| Write the ending part of the instance of a module. More... | |

| void | write_port_binding (const structural_objectRef &port, const structural_objectRef &object_bounded, bool first_port_analyzed) override |

| Write the binding of a port. More... | |

| void | write_vector_port_binding (const structural_objectRef &port, bool first_port_analyzed) override |

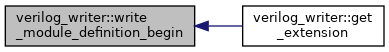

| void | write_module_definition_end (const structural_objectRef &cir) override |

| Write the end part in a module declaration. More... | |

| void | write_io_signal_post_fix (const structural_objectRef &port, const structural_objectRef &sig) override |

| Write some code managing primary ports to signals connections. More... | |

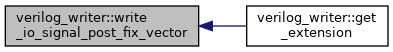

| void | write_io_signal_post_fix_vector (const structural_objectRef &port, const structural_objectRef &sig) override |

| void | write_module_parametrization (const structural_objectRef &cir) override |

| Module can be parameterized with respect different features. More... | |

| void | write_state_declaration (const structural_objectRef &cir, const std::list< std::string > &list_of_states, const std::string &reset_port, const std::string &reset_state, bool one_hot) override |

| write the declaration of all the states of the finite state machine. More... | |

| void | write_present_state_update (const structural_objectRef cir, const std::string &reset_state, const std::string &reset_port, const std::string &clock_port, const std::string &reset_type, bool connect_present_next_state_signals) override |

| write the present_state update process More... | |

| void | write_transition_output_functions (bool single_proc, unsigned int output_index, const structural_objectRef &cir, const std::string &reset_state, const std::string &reset_port, const std::string &start_port, const std::string &clock_port, std::vector< std::string >::const_iterator &first, std::vector< std::string >::const_iterator &end, bool is_yosys, const std::map< unsigned int, std::map< std::string, std::set< unsigned int >>> &bypass_signals) override |

| Write the transition and output functions. More... | |

| void | write_NP_functionalities (const structural_objectRef &cir) override |

| Write in the proper language the behavioral description of the module described in "Not Parsed" form. More... | |

| void | write_port_decl_header () override |

| Write the header for port_decl. More... | |

| void | write_port_decl_tail () override |

| Write the tail for port_decl. More... | |

| void | write_module_parametrization_decl (const structural_objectRef &cir) override |

| Write the declaration of the module parameters. More... | |

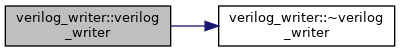

| verilog_writer (const ParameterConstRef parameters) | |

| Constructor. More... | |

| ~verilog_writer () override | |

| Destructor. More... | |

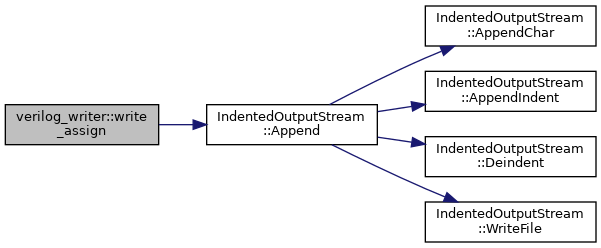

| void | write_assign (const std::string &op0, const std::string &op1) override |

| bool | has_output_prefix () const override |

| bool | check_keyword (const std::string &id) const override |

| void | write_header () override |

| Writes the header part of the file. More... | |

| void | WriteBuiltin (const structural_objectConstRef component) override |

| Write a builtin component. More... | |

Public Member Functions inherited from language_writer Public Member Functions inherited from language_writer | |

| language_writer (char open_char, char close_char, const ParameterConstRef parameters) | |

| Constructor. More... | |

| virtual | ~language_writer () |

| Destructor. More... | |

| virtual void | write (const std::string &rawString) |

| Writes a raw string into the stream. More... | |

| const std::string | WriteString () const |

| Dump the content of the write as a string. More... | |

| void | WriteFile (const std::string &filename) const |

| Write content to a file. More... | |

| CustomSet< std::string > | GetHDLReservedNames () const |

| Return the names of auxiliary signals which will be used by backend. More... | |

| void | WriteLicense () |

| Write the license. More... | |

Static Public Member Functions | |

| static bool | check_keyword_verilog (const std::string &word) |

Static Public Member Functions inherited from language_writer Static Public Member Functions inherited from language_writer | |

| static language_writerRef | create_writer (HDLWriter_Language language, const technology_managerConstRef TM, const ParameterConstRef parameters) |

| Creates the specialization of the writer based on the desired language. More... | |

| static unsigned int | bitnumber (unsigned long long n) |

| Counts the number of bits in an unsigned int. More... | |

Static Protected Attributes | |

| static const std::map< std::string, std::string > | builtin_to_verilog_keyword |

| map putting into relation standard gates with the corresponding built-in Verilog statements. More... | |

| static const std::set< std::string > | keywords |

Additional Inherited Members | |

Protected Member Functions inherited from language_writer Protected Member Functions inherited from language_writer | |

| std::string | encode_one_hot (unsigned int n_states, unsigned int val) const |

Protected Attributes inherited from language_writer Protected Attributes inherited from language_writer | |

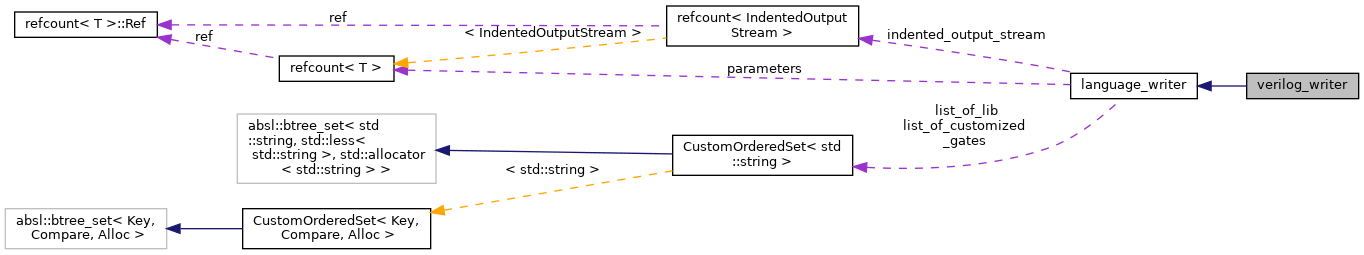

| const IndentedOutputStreamRef | indented_output_stream |

| Represents the stream we are currently writing to. More... | |

| CustomOrderedSet< std::string > | list_of_lib |

| list of library imported (e.g., includes). More... | |

| CustomOrderedSet< std::string > | list_of_customized_gates |

| list of customized gates More... | |

| const ParameterConstRef | parameters |

| the set of input parameters More... | |

| int | debug_level |

| debugging level of the class More... | |

Definition at line 55 of file verilog_writer.hpp.

|

explicit |

Constructor.

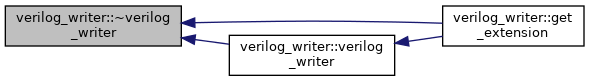

Definition at line 2229 of file verilog_writer.cpp.

References language_writer::debug_level, GET_CLASS, language_writer::parameters, and ~verilog_writer().

Referenced by get_extension().

|

overridedefault |

Destructor.

Referenced by get_extension(), and verilog_writer().

|

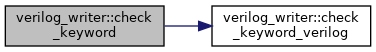

overridevirtual |

Implements language_writer.

Definition at line 2237 of file verilog_writer.cpp.

References check_keyword_verilog().

Referenced by has_output_prefix().

|

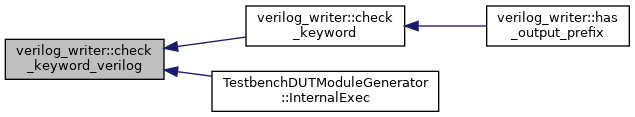

static |

Definition at line 2242 of file verilog_writer.cpp.

References keywords.

Referenced by check_keyword(), and TestbenchDUTModuleGenerator::InternalExec().

|

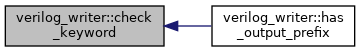

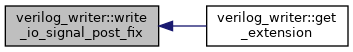

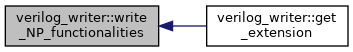

inlineoverridevirtual |

Return the filename extension associated with the verilog_writer.

Implements language_writer.

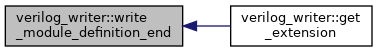

Definition at line 76 of file verilog_writer.hpp.

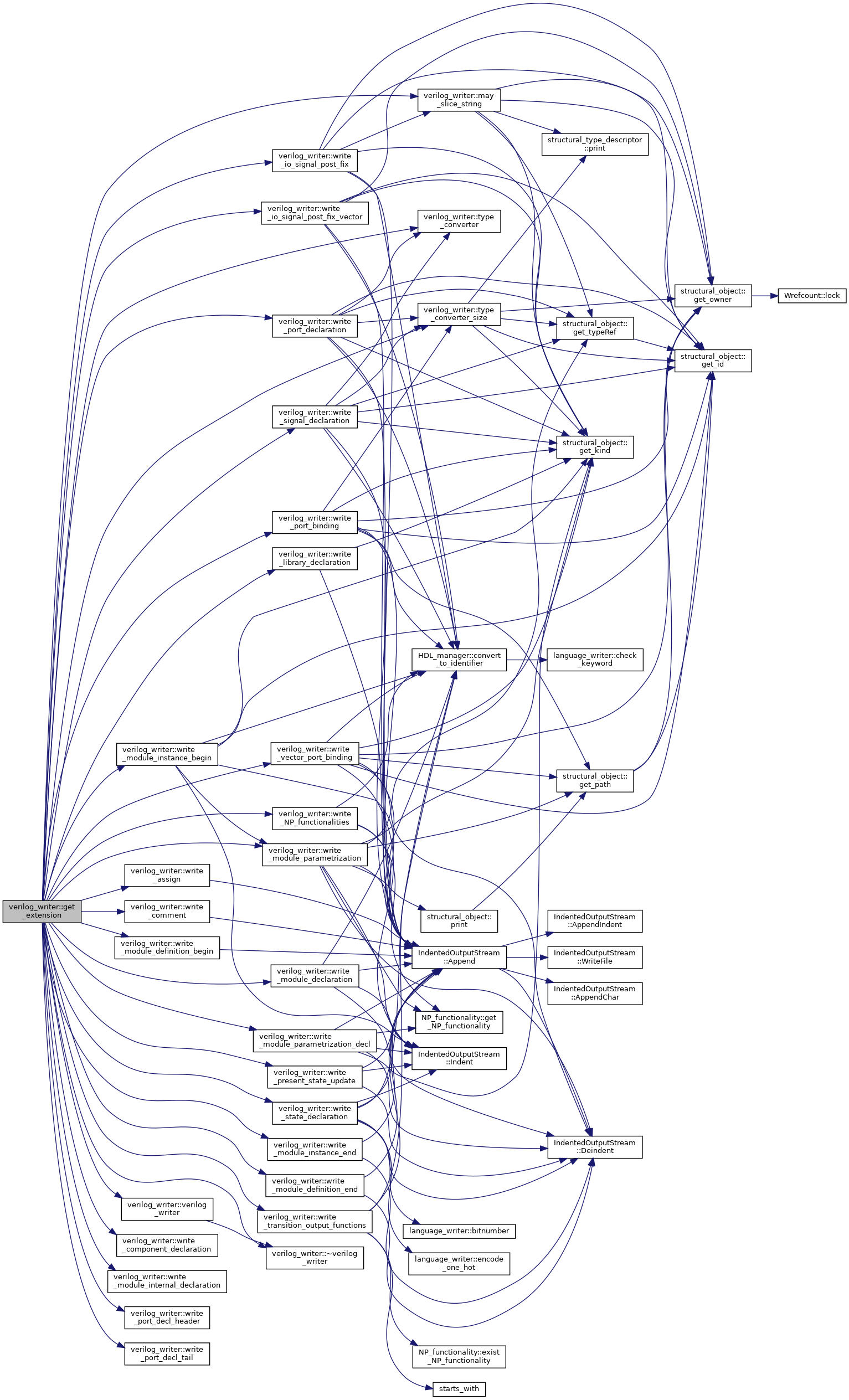

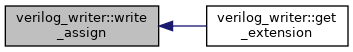

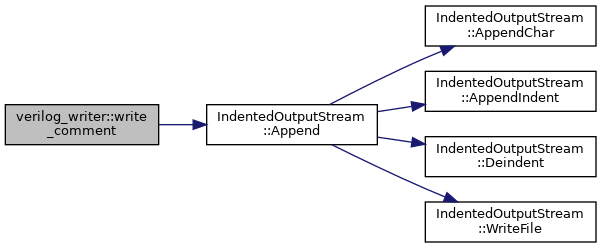

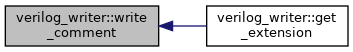

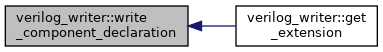

References map, may_slice_string(), language_writer::parameters, type_converter(), type_converter_size(), verilog_writer(), write_assign(), write_comment(), write_component_declaration(), write_io_signal_post_fix(), write_io_signal_post_fix_vector(), write_library_declaration(), write_module_declaration(), write_module_definition_begin(), write_module_definition_end(), write_module_instance_begin(), write_module_instance_end(), write_module_internal_declaration(), write_module_parametrization(), write_module_parametrization_decl(), write_NP_functionalities(), write_port_binding(), write_port_decl_header(), write_port_decl_tail(), write_port_declaration(), write_present_state_update(), write_signal_declaration(), write_state_declaration(), write_transition_output_functions(), write_vector_port_binding(), and ~verilog_writer().

|

inlineoverridevirtual |

Return the name of the language writer.

Implements language_writer.

Definition at line 69 of file verilog_writer.hpp.

|

inlineoverridevirtual |

Implements language_writer.

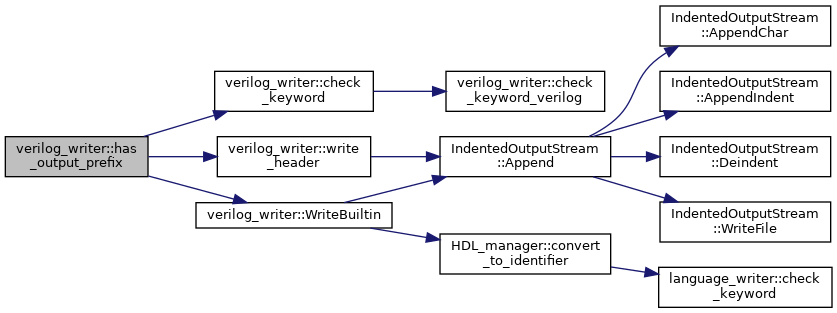

Definition at line 258 of file verilog_writer.hpp.

References check_keyword(), write_header(), and WriteBuiltin().

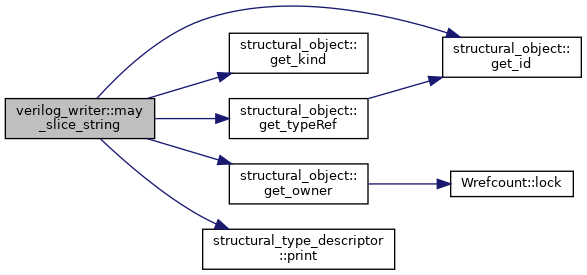

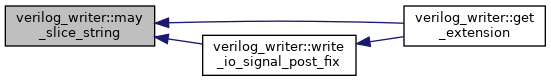

| std::string verilog_writer::may_slice_string | ( | const structural_objectRef & | cir | ) |

return the slice in case of a port owned by a port vector

| port | is the port |

Definition at line 350 of file verilog_writer.cpp.

References BITSIZE_PREFIX, structural_type_descriptor::BOOL, structural_object::get_id(), structural_object::get_kind(), structural_object::get_owner(), structural_object::get_typeRef(), structural_type_descriptor::INT, lenet_tvm::mod, NUM_ELEM_PREFIX, structural_type_descriptor::OTHER, port_vector_o_K, structural_type_descriptor::print(), structural_type_descriptor::REAL, structural_type_descriptor::size, STR, THROW_ERROR, structural_type_descriptor::type, structural_type_descriptor::UINT, structural_type_descriptor::UNKNOWN, structural_type_descriptor::USER, structural_type_descriptor::VECTOR_BOOL, structural_type_descriptor::VECTOR_INT, structural_type_descriptor::VECTOR_REAL, structural_type_descriptor::vector_size, structural_type_descriptor::VECTOR_UINT, and structural_type_descriptor::VECTOR_USER.

Referenced by get_extension(), and write_io_signal_post_fix().

|

overridevirtual |

Return a language based type string given a structural_type_descriptor.

In case of arrays the range of the array is print by the type_converter_size function.

| Type | is the structural_type_descriptor. |

Implements language_writer.

Definition at line 118 of file verilog_writer.cpp.

References structural_type_descriptor::BOOL, structural_type_descriptor::id_type, structural_type_descriptor::INT, structural_type_descriptor::OTHER, structural_type_descriptor::REAL, THROW_ERROR, structural_type_descriptor::type, structural_type_descriptor::UINT, structural_type_descriptor::UNKNOWN, structural_type_descriptor::USER, structural_type_descriptor::VECTOR_BOOL, structural_type_descriptor::VECTOR_INT, structural_type_descriptor::VECTOR_REAL, structural_type_descriptor::VECTOR_UINT, and structural_type_descriptor::VECTOR_USER.

Referenced by get_extension(), write_port_declaration(), and write_signal_declaration().

|

overridevirtual |

Return a language based type string given a structural_type_descriptor for the range of the array.

In case of scalar type it return an empty string.

| cir | is the object for which the size has been computed. |

Implements language_writer.

Definition at line 175 of file verilog_writer.cpp.

References BITSIZE_PREFIX, structural_type_descriptor::BOOL, structural_object::get_id(), structural_object::get_kind(), structural_object::get_owner(), GET_TYPE_SIZE, structural_object::get_typeRef(), structural_type_descriptor::id_type, structural_type_descriptor::INT, lenet_tvm::mod, NUM_ELEM_PREFIX, structural_type_descriptor::OTHER, port_vector_o_K, PORTSIZE_PREFIX, structural_type_descriptor::print(), structural_type_descriptor::REAL, signal_vector_o_K, structural_type_descriptor::size, STR, THROW_ERROR, THROW_UNREACHABLE, structural_type_descriptor::type, structural_type_descriptor::UINT, structural_type_descriptor::UNKNOWN, structural_type_descriptor::USER, structural_type_descriptor::VECTOR_BOOL, structural_type_descriptor::VECTOR_INT, structural_type_descriptor::VECTOR_REAL, structural_type_descriptor::vector_size, structural_type_descriptor::VECTOR_UINT, and structural_type_descriptor::VECTOR_USER.

Referenced by get_extension(), write_port_binding(), write_port_declaration(), and write_signal_declaration().

|

overridevirtual |

Implements language_writer.

Definition at line 546 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), and language_writer::indented_output_stream.

Referenced by get_extension().

|

overridevirtual |

Print a comment.

| comment_string | is the string to be printed as a comment. |

Implements language_writer.

Definition at line 113 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), and language_writer::indented_output_stream.

Referenced by get_extension().

|

overridevirtual |

Write the declaration of a component.

| cir | is the component to be declared. |

Implements language_writer.

Definition at line 594 of file verilog_writer.cpp.

Referenced by get_extension().

|

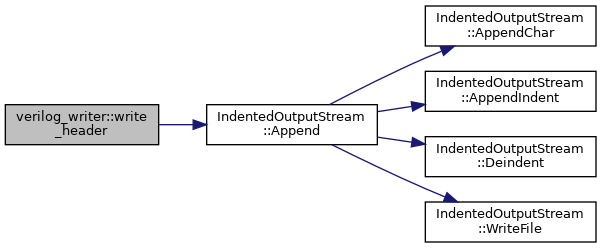

overridevirtual |

Writes the header part of the file.

Write some lines of comments and possibly global libraries.

Reimplemented from language_writer.

Definition at line 2247 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), and language_writer::indented_output_stream.

Referenced by has_output_prefix().

|

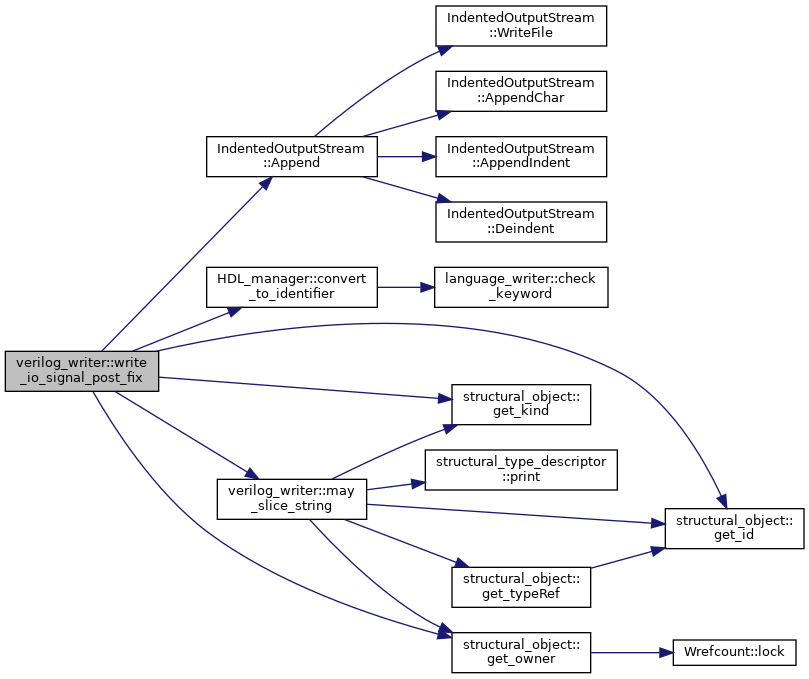

overridevirtual |

Write some code managing primary ports to signals connections.

Loop signals are present for example in this bench circuit: INPUT(X) OUTPUT(Z) Y = DFF(Z) Z = AND(X,Y). The circuit builder adds an internal signal Z_sign allowing the write and read of the Z values. In verilog, this problem has been solved in this way: ???;

| port | is the primary port for which this problem happens. |

| sig | is the attached signal. |

Implements language_writer.

Definition at line 1018 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), constant_o_K, HDL_manager::convert_to_identifier(), structural_object::get_id(), structural_object::get_kind(), structural_object::get_owner(), GET_TYPE_SIZE, language_writer::indented_output_stream, may_slice_string(), port_o_K, port_vector_o_K, signal_o_K, signal_vector_o_K, STR, and THROW_ASSERT.

Referenced by get_extension().

|

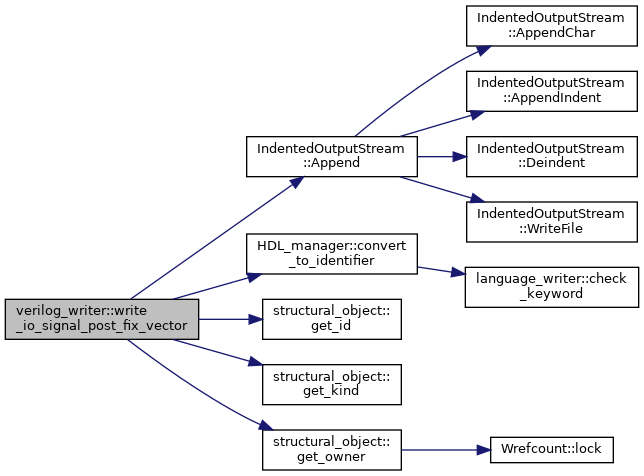

overridevirtual |

Implements language_writer.

Definition at line 1066 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), HDL_manager::convert_to_identifier(), structural_object::get_id(), structural_object::get_kind(), structural_object::get_owner(), language_writer::indented_output_stream, port_vector_o_K, signal_vector_o_K, and THROW_ASSERT.

Referenced by get_extension().

|

overridevirtual |

Write the #include for each used library.

| cir | is the component for which the library declarations are written. |

Implements language_writer.

Definition at line 487 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), channel_o_K, component_o_K, structural_object::get_kind(), language_writer::indented_output_stream, NP_functionality::IP_INCLUDE, and THROW_ASSERT.

Referenced by get_extension().

|

overridevirtual |

Write the declaration of the module.

| cir | is the module to be written. |

write IO port declarations respecting the position

Implements language_writer.

Definition at line 503 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), HDL_manager::convert_to_identifier(), IndentedOutputStream::Deindent(), GET_TYPE_NAME, IndentedOutputStream::Indent(), language_writer::indented_output_stream, lenet_tvm::mod, register_AR_NORETIME, register_AR_NORETIME_INT, register_AR_NORETIME_REAL, register_AR_NORETIME_UINT, and THROW_ASSERT.

Referenced by get_extension().

|

overridevirtual |

Write the top constructor declaration.

| cir | is the top component to be declared. |

Implements language_writer.

Definition at line 616 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), and language_writer::indented_output_stream.

Referenced by get_extension().

|

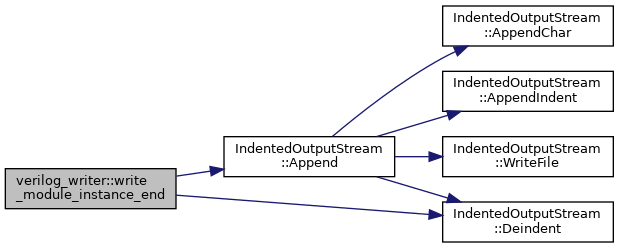

overridevirtual |

Write the end part in a module declaration.

| cir | is the top component to be declared. |

Implements language_writer.

Definition at line 710 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), IndentedOutputStream::Deindent(), and language_writer::indented_output_stream.

Referenced by get_extension().

|

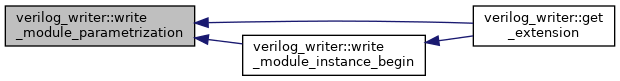

overridevirtual |

Write the initial part of the instance of a module.

| cir | is the module to be instanced. |

| component_name | is the name of the module to be instanced. It has to be specified since VHDL and verilog can print in different ways |

| write_parametrization | specified if parameters have to be written |

check possible module parametrization

Implements language_writer.

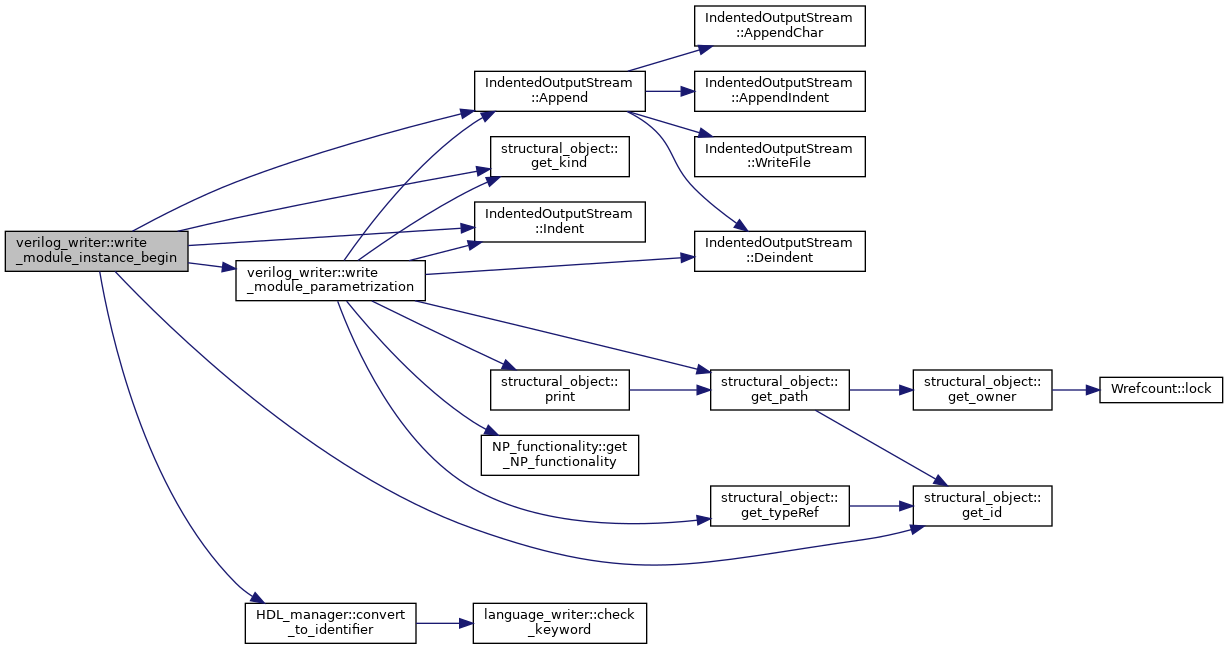

Definition at line 682 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), channel_o_K, component_o_K, HDL_manager::convert_to_identifier(), structural_object::get_id(), structural_object::get_kind(), IndentedOutputStream::Indent(), language_writer::indented_output_stream, THROW_ASSERT, and write_module_parametrization().

Referenced by get_extension().

|

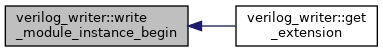

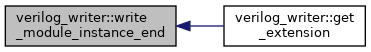

overridevirtual |

Write the ending part of the instance of a module.

| cir | is the module to be instanced. |

Implements language_writer.

Definition at line 704 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), IndentedOutputStream::Deindent(), and language_writer::indented_output_stream.

Referenced by get_extension().

|

overridevirtual |

Write the declaration of internal objects of the module.

| cir | is the module to be written. |

Implements language_writer.

Definition at line 542 of file verilog_writer.cpp.

Referenced by get_extension().

|

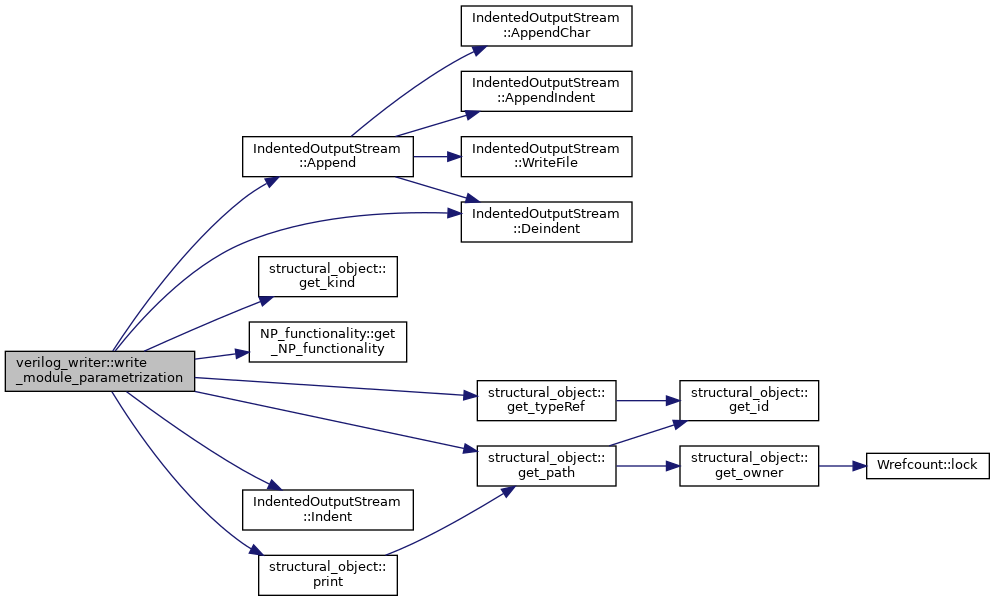

overridevirtual |

Module can be parameterized with respect different features.

Port vectors areparameterizedd with the number of port associated, while ports are parameterized in case the type is a integer with the number of bits. The id of the module is modified by adding the parameters at its end. For example an AND_GATE with a port_vector of 2 will be declared as: AND_GATE_2. Moreover, a multiplier with the first input of four bits, the second input with eight bits and an output of twelve bits will be declared as: MULT_4_8_12. Note that parametrization has a meaning only in case the functionality come from the STD technology library.

| cir | is the component to be declared. |

writing memory-related parameters

Implements language_writer.

Definition at line 1085 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), BITSIZE_PREFIX, channel_o_K, component_o_K, language_writer::debug_level, DEBUG_LEVEL_VERY_PEDANTIC, IndentedOutputStream::Deindent(), structural_object::get_kind(), NP_functionality::get_NP_functionality(), structural_object::get_path(), GET_TYPE_SIZE, structural_object::get_typeRef(), IndentedOutputStream::Indent(), INDENT_DBG_MEX, language_writer::indented_output_stream, MEMORY_PARAMETER, lenet_tvm::mod, NUM_ELEM_PREFIX, port_vector_o_K, PORTSIZE_PREFIX, structural_object::print(), structural_type_descriptor::size, STR, THROW_ASSERT, THROW_ERROR, structural_type_descriptor::type, test_panda::type, symmetry::value, structural_type_descriptor::VECTOR_INT, structural_type_descriptor::VECTOR_REAL, structural_type_descriptor::vector_size, and structural_type_descriptor::VECTOR_UINT.

Referenced by get_extension(), and write_module_instance_begin().

|

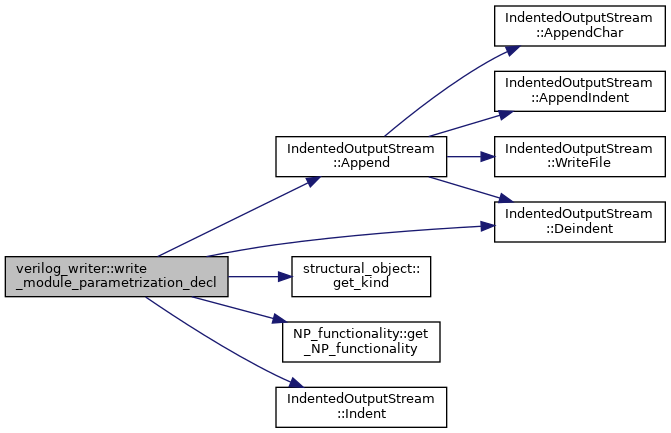

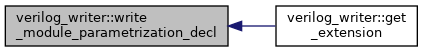

overridevirtual |

Write the declaration of the module parameters.

writing memory-related parameters

FIXME: this is workaround due to the fact that the default value of MEMORY_PARAMETER is ""

writing other library parameters

if at least one parameter is used, first_it is true.

Implements language_writer.

Definition at line 2114 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), BITSIZE_PREFIX, channel_o_K, component_o_K, language_writer::debug_level, DEBUG_LEVEL_VERY_PEDANTIC, IndentedOutputStream::Deindent(), structural_object::get_kind(), NP_functionality::get_NP_functionality(), GET_TYPE_SIZE, IndentedOutputStream::Indent(), INDENT_DBG_MEX, language_writer::indented_output_stream, MEMORY_PARAMETER, lenet_tvm::mod, NUM_ELEM_PREFIX, param, port_vector_o_K, PORTSIZE_PREFIX, PRINT_DBG_MEX, STR, THROW_ASSERT, test_panda::type, symmetry::value, structural_type_descriptor::VECTOR_INT, structural_type_descriptor::VECTOR_REAL, and structural_type_descriptor::VECTOR_UINT.

Referenced by get_extension().

|

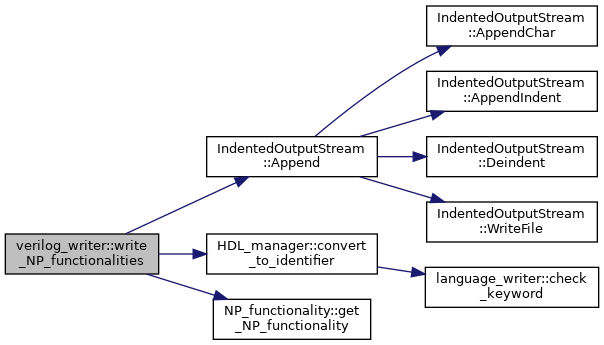

overridevirtual |

Write in the proper language the behavioral description of the module described in "Not Parsed" form.

| cir | is the component. |

manage reset by preprocessing the behavioral description

Implements language_writer.

Definition at line 2056 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), HDL_manager::convert_to_identifier(), NP_functionality::get_NP_functionality(), GET_TYPE_NAME, language_writer::indented_output_stream, lenet_tvm::mod, language_writer::parameters, RESET_PORT_NAME, THROW_ASSERT, and NP_functionality::VERILOG_PROVIDED.

Referenced by get_extension().

|

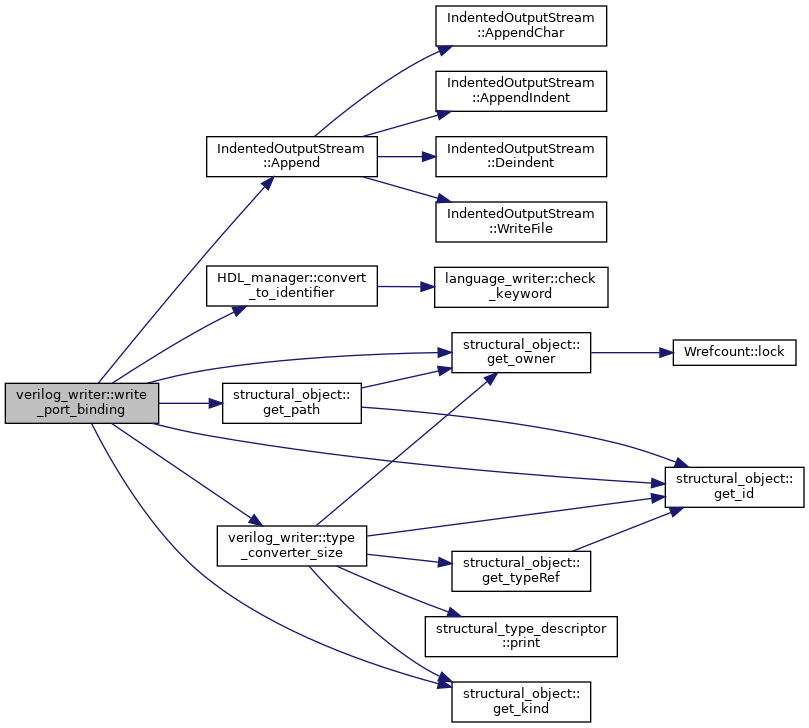

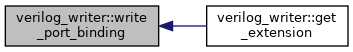

overridevirtual |

Write the binding of a port.

It follows the name binding style.

| port | is the port to be bounded. |

| top | is the component owner of the component that has the port to be bounded. |

Implements language_writer.

Definition at line 961 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), constant_o_K, HDL_manager::convert_to_identifier(), structural_object::get_id(), structural_object::get_kind(), structural_object::get_owner(), structural_object::get_path(), GET_TYPE_SIZE, language_writer::indented_output_stream, port_o_K, port_vector_o_K, signal_o_K, signal_vector_o_K, STR, THROW_ASSERT, and type_converter_size().

Referenced by get_extension().

|

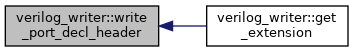

overridevirtual |

Write the header for port_decl.

do nothing

Implements language_writer.

Definition at line 2104 of file verilog_writer.cpp.

Referenced by get_extension().

|

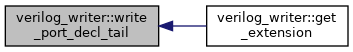

overridevirtual |

Write the tail for port_decl.

do nothing

Implements language_writer.

Definition at line 2109 of file verilog_writer.cpp.

Referenced by get_extension().

|

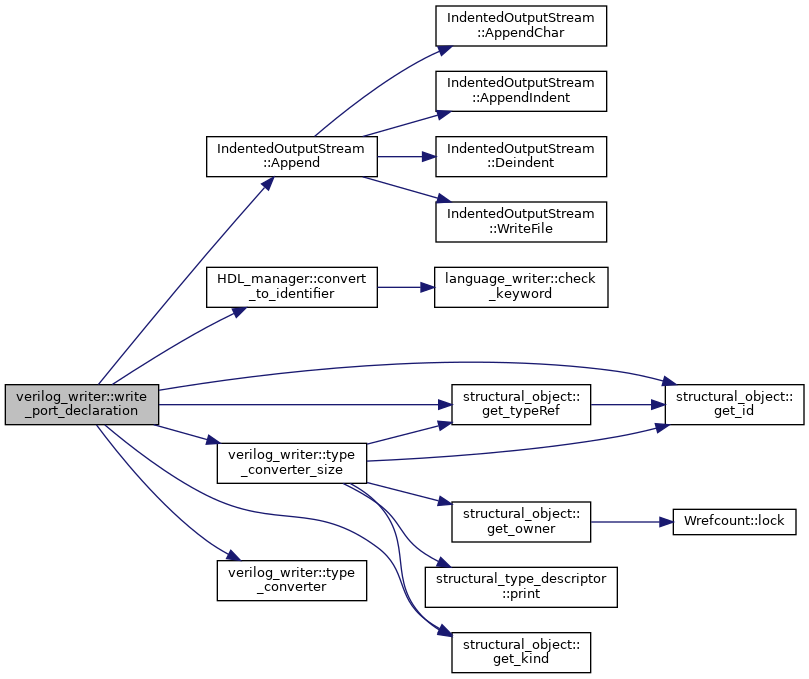

overridevirtual |

Write the port declaration starting from a port object.

| cir | is the port to be written. |

Implements language_writer.

Definition at line 554 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), HDL_manager::convert_to_identifier(), structural_object::get_id(), structural_object::get_kind(), structural_object::get_typeRef(), language_writer::indented_output_stream, port_o_K, port_vector_o_K, THROW_ASSERT, THROW_ERROR, type_converter(), and type_converter_size().

Referenced by get_extension().

|

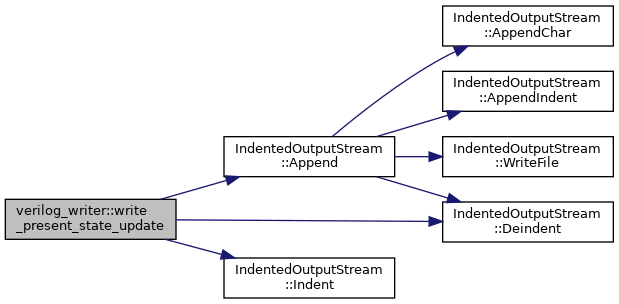

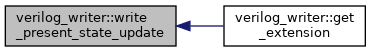

overridevirtual |

write the present_state update process

| reset_state | is the reset state. |

| reset_port | is the reset port. |

| clock_port | is the clock port. |

| reset_type | specify the type of the reset |

reset is needed even in case of reset_type == "no"

Implements language_writer.

Definition at line 1351 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), IndentedOutputStream::Deindent(), NP_functionality::FSM_CS, IndentedOutputStream::Indent(), language_writer::indented_output_stream, lenet_tvm::mod, NEXT_STATE_PORT_NAME, language_writer::parameters, PRESENT_STATE_PORT_NAME, SELECTOR_REGISTER_FILE, and STR.

Referenced by get_extension().

|

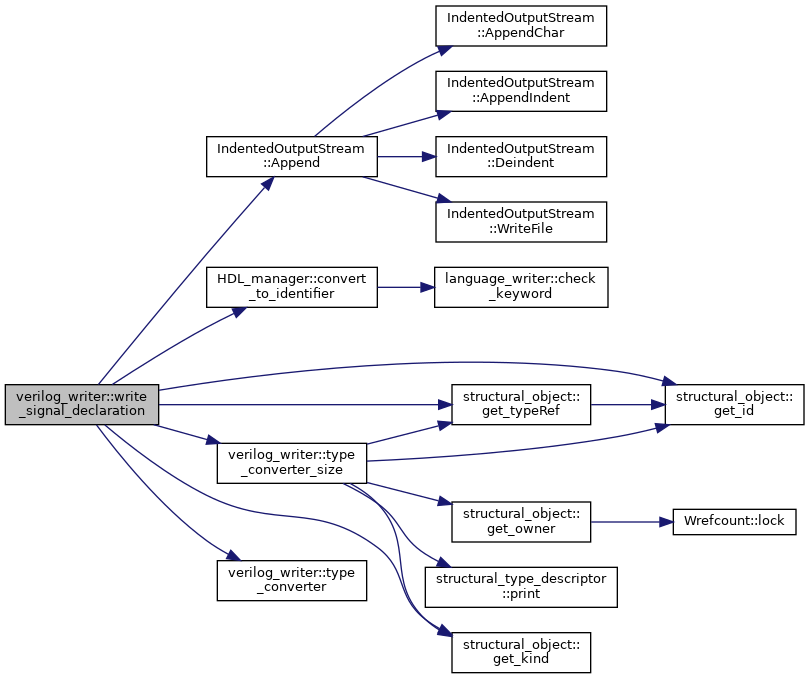

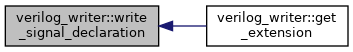

overridevirtual |

Write the declaration of a signal.

| cir | is the signal to be declared. |

Implements language_writer.

Definition at line 598 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), structural_type_descriptor::BOOL, HDL_manager::convert_to_identifier(), structural_object::get_id(), structural_object::get_kind(), structural_object::get_typeRef(), language_writer::indented_output_stream, signal_o_K, signal_vector_o_K, structural_type_descriptor::size, STR, THROW_ASSERT, structural_type_descriptor::type, type_converter(), type_converter_size(), and structural_type_descriptor::vector_size.

Referenced by get_extension().

|

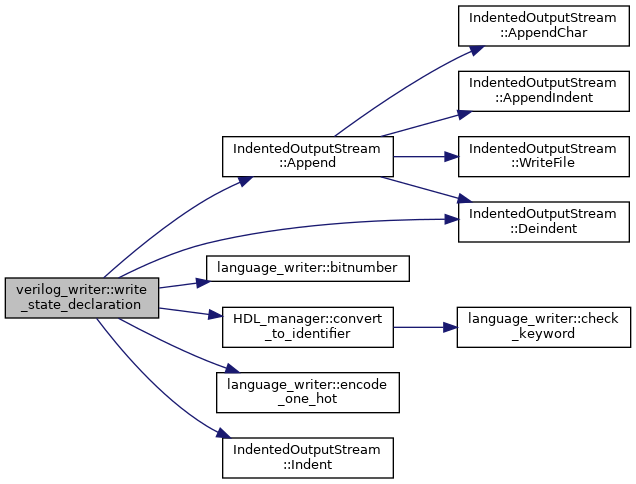

overridevirtual |

write the declaration of all the states of the finite state machine.

| list_of_states | is the list of all the states. |

adjust in case states are not consecutive

enable buffers

Implements language_writer.

Definition at line 1220 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), language_writer::bitnumber(), HDL_manager::convert_to_identifier(), language_writer::debug_level, DEBUG_LEVEL_VERBOSE, IndentedOutputStream::Deindent(), language_writer::encode_one_hot(), NP_functionality::FSM_CS, IndentedOutputStream::Indent(), language_writer::indented_output_stream, max, lenet_tvm::mod, NEXT_STATE_PORT_NAME, language_writer::parameters, PRESENT_STATE_PORT_NAME, PRINT_DBG_MEX, STATE_NAME_PREFIX, STR, and THROW_ASSERT.

Referenced by get_extension().

|

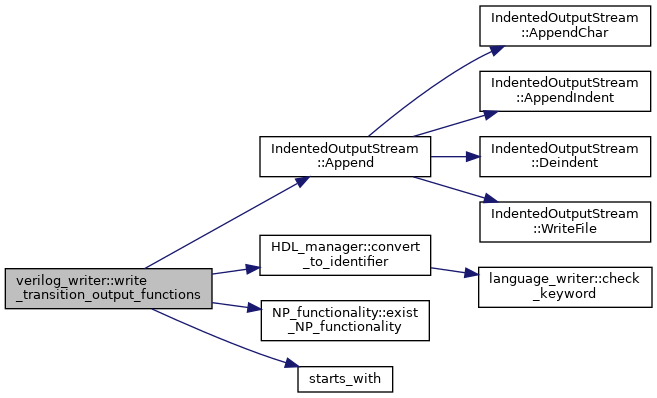

overridevirtual |

Write the transition and output functions.

| cir | is the component. |

| reset_port | is the reset port. |

| clock_port | is the clock port. |

| first | is the first iterator of the state table. |

| end | is the end iterator of the state table. |

| is_yosys | is true when the transition table is meant for YOSYS. |

state transitions description

default next_state when multi-process FSMs are considered

compute the default output

get the present state

get the current output

check if we can skip this state

check unique-case condition

Implements language_writer.

Definition at line 1405 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), HDL_manager::convert_to_identifier(), language_writer::debug_level, DEBUG_LEVEL_VERY_PEDANTIC, NP_functionality::exist_NP_functionality(), NP_functionality::FSM_CS, INDENT_DBG_MEX, language_writer::indented_output_stream, lenet_tvm::mod, NEXT_STATE_PORT_NAME, language_writer::parameters, PRESENT_STATE_PORT_NAME, SELECTOR_REGISTER_FILE, starts_with(), STD_CLOSING_CHAR, STD_OPENING_CHAR, STR, THROW_ASSERT, and THROW_ERROR.

Referenced by get_extension().

|

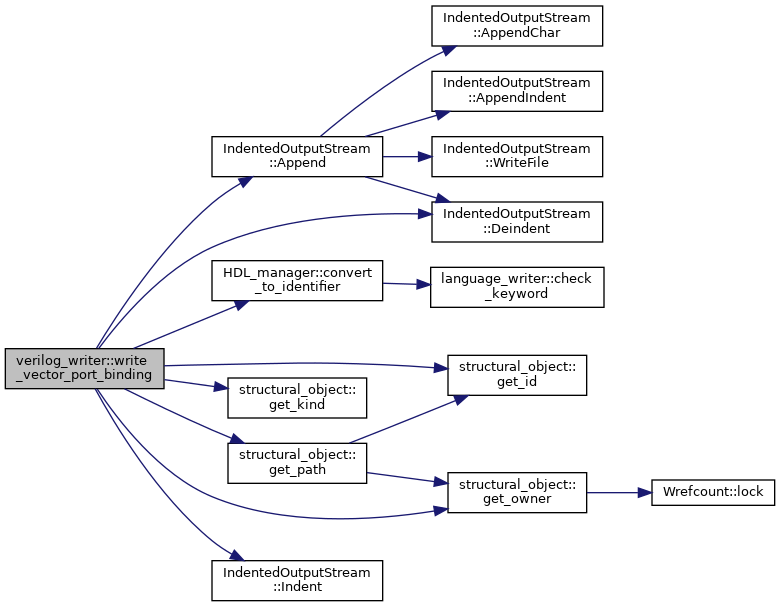

overridevirtual |

Implements language_writer.

Definition at line 716 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), constant_o_K, HDL_manager::convert_to_identifier(), language_writer::debug_level, DEBUG_LEVEL_VERY_PEDANTIC, IndentedOutputStream::Deindent(), structural_object::get_id(), structural_object::get_kind(), structural_object::get_owner(), structural_object::get_path(), GET_TYPE_SIZE, IndentedOutputStream::Indent(), INDENT_DBG_MEX, language_writer::indented_output_stream, index, max, port_vector_o_K, signal_vector_o_K, STR, THROW_ASSERT, and THROW_ERROR.

Referenced by get_extension().

|

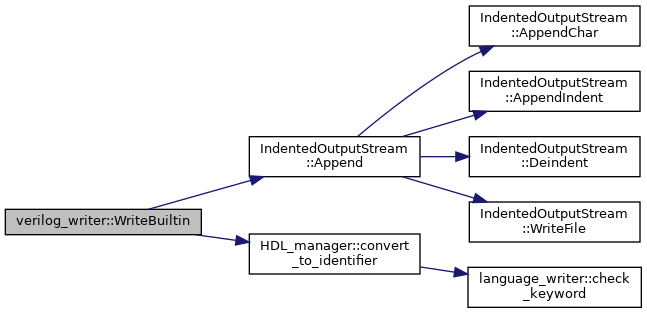

overridevirtual |

Write a builtin component.

| component | is the component to be printed |

Implements language_writer.

Definition at line 621 of file verilog_writer.cpp.

References IndentedOutputStream::Append(), builtin_to_verilog_keyword, HDL_manager::convert_to_identifier(), GET_TYPE_NAME, language_writer::indented_output_stream, lenet_tvm::mod, port_o_K, port_vector_o_K, STR, THROW_ASSERT, and THROW_UNREACHABLE.

Referenced by has_output_prefix().

|

staticprotected |

map putting into relation standard gates with the corresponding built-in Verilog statements.

Definition at line 59 of file verilog_writer.hpp.

Referenced by WriteBuiltin().

|

staticprotected |

Definition at line 61 of file verilog_writer.hpp.

Referenced by check_keyword_verilog().

1.8.13

1.8.13